## Science and Technology English I

Exercise 113 Meiji University 2021 (DICS Chapter 3-3, Ring Oscillator Continued) EX\_113\_21.pptx 15 Slides March 27<sup>th.</sup>,2021

http://mikami.a.la9.jp/mdc/mdc1.htm

## Renji Mikami

Renji\_Mikami(at\_mark)nifty.com [mikami(at\_mark)meiji.ac.jp]

# (Day 11) インバーターからの展開

- CMOS回路 -> 反転回路

- 反転回路 => インバータ

- インバータを多入力化 => 論理回路化 NAND/NOR

- インバータの出力を入力にフィードバック

- ⇒リングオシレータ(発振回路)へ: Day 12>13のテーマ

- ⇒さらに 発信回路は、クロックに展開

- ⇒クロックから、同期回路の構成へ: 秋学期に続きます

- ⇒同期回路の高速化、パイプラインへ: 秋学期に続きます

- ⇒同期回路の安定動作、メタステーブル: 秋学期に続きます

# Technical Term "topology"

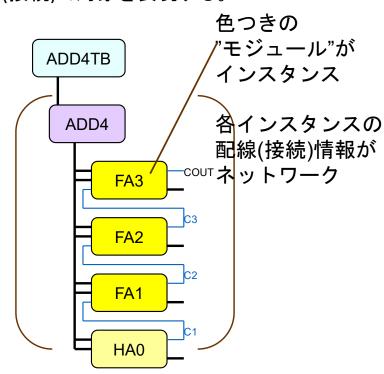

- EX\_113 で topology という単語が出てきます。これは、 (physical structure / instance and network というニュアンスで) behavior に対する概念で使われます。

- ・無理に日本語に訳して解釈しようとすると無理が生じます。Behaviorとの対比でイメージ(概念)的に理解するとうまくいきます。

- HDLと回路図の対比で具体的に解説します。

- Behavior は"動作"あるは"振舞い"です

- Topology は"具体的な回路要素とその接続"です

# 4 bit 加算器の Topology / Behavior 表現

Add4のTopology (Structure –構造) 記述例: インスタンス(要素/素子)とネット ワーク(接続)で対象を表現する。

Add4 のbehavior (ふるまい、動作) 記述例(HDL記述)

A[a0..a3]

B[b0..b3]

Y[y0..y3]

Y = A + B;

秋学期: EX 209 から

# Exercise: EX\_113

- EX\_113-1 から3を通読して和文または英文で要旨をまとめる。

- 自動翻訳は、課題文ごとに表示してある。

- 提出はClass Web "レポート" にて木曜まで

- 毎回のレポートは、最低A41ページ以上は書いてください。余白には、 今回の授業の内容、資料についての感想や要望を記入してください。

自動翻訳は、excite (<a href="https://www.excite.co.jp/world/english/">https://www.excite.co.jp/world/english/</a>) を使用 Day 14 試験について

#### EX\_113-1 p117 [STE-101-309]

#### 通読して和文または英文で要旨をまとめてください

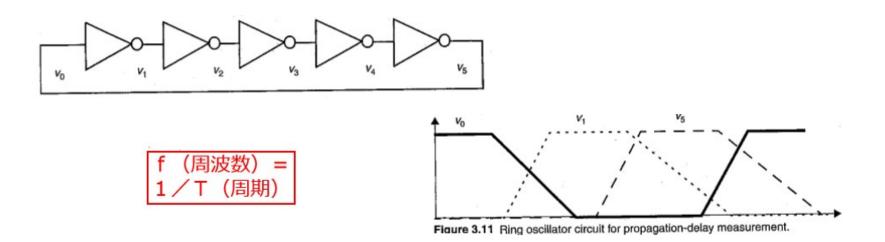

The propagation delay of a gate is, a function of its fan-in and fan-out. Fan-out gates present an increased load (mostly capacitive) to the driving gate and slow its performance. The increased complexity of a gate due to a large fan-in also has a negative influence on the performance. When comparing the performance of gates in different technologies, it is important not to confuse the picture by including second-order parameters such as fan-in and fan-out. It is therefore useful to find a uniform way of measuring the tp of a gate, so that technologies can be judged on an equal footing. The de-facto standard circuit for delay measurement is the ring oscillator, which consists of an odd number of inverters connected in a circular chain (Figure 3.11). Due to the odd number of inversions, this circuit does not have a stable operating point and oscillates.

1 The 50% definition is inspired the assumption that the switching threshold VM is typically located in the middle of the logic swing.

EX\_113-1 p1: [STE-101-309]

the 10% and 90% points of the waveforms (Figure 3.10).

The propagation delay of a gate is a function of its fan-in and fan-out. Fan-out gates present an increased load (mostly capacitive) to the driving gate and slow its performance. The increased complexity of a gate due to a large fan-in also has a negative influence on the performance. When comparing the performance of gates in different technologies, it is important not to confuse the picture by including second-order parameters such as fan-in and fan-out. It is therefore useful to find a uniform way of measuring the  $t_p$  of a gate, so that technologies can be judged on an equal footing. The de-facto standard circuit for delay measurement is the ring oscillator, which consists of an odd number of inverters connected in a circular chain (Figure 3.11). Due to the odd number of inversions, this circuit does not have a stable operating point and oscillates. The period T of the oscillation is determined by the propagation time of a signal transition through the complete chain, or

The 50% definition is inspired the assumption that the switching threshold  $V_M$  is typically located in the middle of the logic swing.

## EX\_113-1 p117 [STE-101-309] **自動翻訳**

ゲートの信号伝播時間はファンインとファンアウトの機能である。ファンアウトゲートは、ドライブゲートおよび遅さそのパフォーマンスに、増大したロード(たいてい、静電容量である)を示す。大きいファンインによるゲートの増大したcomplexcityは、性能へのネガティブな影響も持っている。種々のテクノロジーのゲートの性能を比較する時には、写真を、ファンインやファンアウトなどの二番目注文パラメータを含むことと混同しないことが重要である。従って、ゲートのtpを測定するための均一な方法を見つけることが有益である。対等の立場でテクノロジーが判断されうるように。遅延測定のための不事実標準回路はリング発振器である。それは、丸いチェーンにおいて接続されたインバーターの奇数から成る(図3.11)。逆転の奇数のため、この回路は操作して安定していて一理なく、発振する。

https://www.excite.co.jp/world/english/

#### EX\_113-2 p118 [STE-101-309 line 22~ P119[STE-101-310 line 5]

#### 通読して和文または英文で要旨をまとめてください

The period T of the oscillation is determined by the propagation time of a signal transition through the complete chain, or T = 2 x tp x N with N the number of inverters in the chain. The factor 2 results from the observation that a full cycle requires both a low-to-high and a high-to-low transition. Note that this equation is only valid for 2Ntp >> tf + tr If this condition is not met, the circuit might not oscillate—one "wave" of signals propagating through the ring will overlap with a successor and eventually dampen the oscillation. Typically, a ring oscillator needs a least five stages to be operational.

EX\_113- 2 p118 [STE-101 -309 line 22~ P119[STE-101 -310 line 5]

STE-101-310

EX\_113\_21

The period T of the oscillation is

determined by the propagation time of a signal transition through the complete chain, or  $T = 2 \times t_p \times N$  with N the number of inverters in the chain. The factor 2 results from the observation that a full cycle requires both a low-to-high and a high-to-low transition. Note that this equation is only valid for  $2Nt_p >> t_f + t_r$ . If this condition is not met, the circuit might not oscillate—one "wave" of signals propagating through the ring will overlap with a successor and eventually dampen the oscillation. Typically, a ring oscillator needs a least five stages to be operational.

# EX\_113-2 p118 [STE-101-309 line 22~ P119[STE-101-310 line 5]**自動翻訳**

- 振動の期間Tは、Nによって完全なチェーンを通るシグナルの変遷の伝播時間、またはT = 2 X tp X Nによって決定されるチェーンのインバーターの数。

- ファクター2は、完全なサイクルが低にの高さおよび高にで低い変遷必要とする観察に起因している。

- もしこの条件が満たされず、リングに伝わっているシグナルの回路不発振1の「波」が後継者と重なり、結局、振動を湿らすならば、2Ntp >> tf+tr.のためにこの方程式が有効であることにだけ注意しなさい。

- 一般に、稼動可能であるように、リング発振器には最もわずかな5の段 階が必要である。

https://www.excite.co.jp/world/english/

### EX\_113-3 p118 [STE-101-310] line 7 ~17

#### 通読して和文または英文で要旨をまとめてください

We must be extremely careful with results obtained from ring oscillator measurements. A tp of 100 psec by no means implies that a circuit built with those gates will operate at 10 GHz. The oscillator results are primarily useful for quantifying the differences between various manufacturing technologies and gate topologies. The oscillator is an idealized circuit where each gate has a fan-in and fan-out of exactly one and parasitic loads are minimal. In more realistic digital circuits, fan-ins and fan-outs are higher, and interconnect delays are non-negligible. The gate functionality is also substantially more complex than a simple invert operation. As a result, the achievable clock frequency on average is 50 to a 100 times slower than the frequency predicted from ring oscillator measurements. This is an average observation; carefully optimized designs might approach the ideal frequency more closely.

#### Example 3.3 Propagation Delay of First-Order RC Network

Digital circuits are often modeled as first-order RC networks of the type shown in Figure 3.12. The propagation delay of such a network is thus of considerable interest.

we must be extremely careful with results obtained from ring oscillator measurements. A  $t_p$  of 100 psec by no means implies that a circuit built with those gates will operate at 10 GHz. The oscillator results are primarily useful for quantifying the differences between various manufacturing technologies and gate topologies. The oscillator is an idealized circuit where each gate has a fan-in and fan-out of exactly one and parasitic loads are minimal. In more realistic digital circuits, fan-ins and fan-outs are higher, and interconnect delays are non-negligible. The gate functionality is also substantialy more complex than a simple invert operation. As a result, the achievable clock frequency on average is 50 to a 100 times slower than the frequency predicted from ring oscillator measurements. This is an average observation; carefully optimized designs might approach the ideal frequency more closely.

### Example 3.3 Propagation Delay of First-Order RC Network

Digital circuits are often modeled as first-order RC networks of the type shown in Figure 3.12. The propagation delay of such a network is thus of considerable interest.

## EX\_113-3 p118 [STE-101-310] line 7~17 [自動翻訳]

私達は、リング発振器寸法から得られた結果に極めて注意しなければならない。100ピコセカンドのtpは、決して、第一に発振器結果が、様々な製造テクノロジーとゲートトポロジーの違いを定量化するのに有益な10 GHz.で、それらのゲートで組み立てられた回路が動作するのを暗示していない。発振器は、個々のゲートがファンインを持ち、ちょうど1のファンアウトおよび寄生的なロードが最小の理想化される回路である。よりリアルなデジタルの回路で、ファンインとファンアウトがより高く、遅延を相互接続する取るに足りなくない。ゲート機能は、より複雑に大幅に1つの結果あたり1回の簡単な逆転のperation.Asよりでもあり、平均の達成可能なクロック周波数は、リング発振器寸法から予測された頻度より100倍遅さに50である。これは平均的な観察である;慎重に最適化されたデザインは、理想的な頻度により密接に近づくことができる。

### Memo

予習:次回の資料に必ず目を通しておいてください。

フォローアップURL (Revised)

http://mikami.a.la9.jp/meiji/MEIJI.htm

担当講師 三上廉司(みかみれんじ) Renji\_Mikami(at\_mark)nifty.com mikami(at\_mark)meiji.ac.jp (Alternative) http://mikami.a.la9.jp/\_edu.htm