# Science and Technology English I

Exercise 112 Meiji University 2021 (DICS Chapter 3-2, Ring Oscillator) EX 112 21.pptx 14 Slides July 8<sup>th.</sup>,2022

http://mikami.a.la9.jp/mdc/mdc1.htm

Renji Mikami

Renji\_Mikami(at\_mark)nifty.com [mikami(at\_mark)meiji.ac.jp]

## Day11 Review

- インバータ回路から論理回路へ

- 接続数(駆動数)

- 入力-ファンイン数

- 出力-ファンアウト数

- トランジスタ(TTL)の場合は10程度、接続が増えるとレベルが甘くなる(ノイズマージンが減ってくる)

- FETの場合は、接続が増えると遅延が増える(配線とゲート容量が増えて充放電時間が増える)

- 論理と信号レベルの対応

- 入力 Viн 論理 1 レベル Vil 論理 0 レベル

- 出力 Voн 論理 1 レベル Vol 論理 0 レベル

- ・ノイズマージン

- HIGH(1)側 VOH VIH, LOW(0)側 VIL VOL

# Day 12 インバーター からの展開

- CMOS回路 -> 反転回路

- 反転回路 = インバータ

- インバータを多入力化 => 論理回路化 NAND/NOR

- インバータの出力を入力にフィードバック

- ⇒リングオシレータ(発振回路)へ: Day 12のテーマ

- ⇒さらに 発信回路は、クロックに展開

- ⇒クロックから、同期回路の構成へ: 秋学期に続きます

- ⇒同期回路の高速化、パイプラインへ: 秋学期に続きます

- ⇒同期回路の安定動作、メタステーブル: 秋学期に続きます

# 技術解説 Ring Oscillator

• B2 論理回路実習で作った"発振回路"

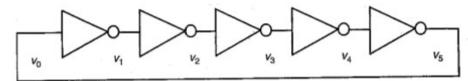

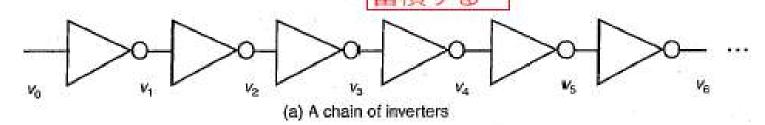

- 奇数段のインバータを直列に接続

- 段数は、遅延時間との兼ね合いで決める

- 遅延時間と段数がタイミング的に合わないと動作しない

- ・これは非同期回路の典型でLSI設計では(原則)使用禁止

- 理由: LSI設計では、遅延時間はレイアウト後に決定するので動作保証できない。 回路の配置やプロセスの変更でも遅延時間が変わる。テスト不能。

- それでも使用するケース:コストが安い、LSI内部にビルトイン・オシレータ回路がない場合、部分的に超高速動作が必要な場合などリスクを管理が必要

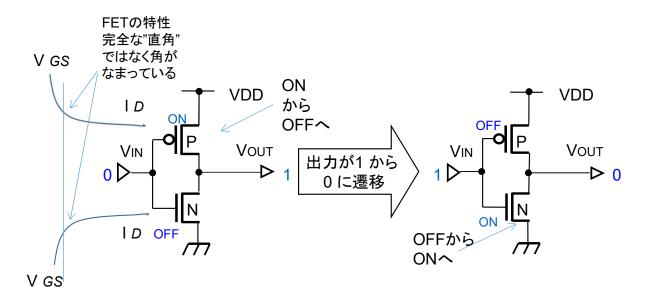

# CMOS インバータ回路と特性

Vout tpH 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 10% - 1

リングオシレータをインバーター段で構成した場合、回路動作の 遅延のためインバータの出力(Vout)が反転する前の状態が 入力(Vin)に帰還されてしまいます。

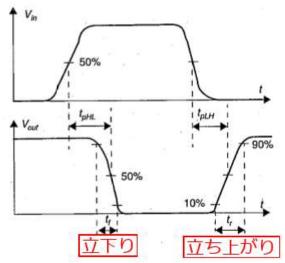

tr: rise time, tf: fall time, tp/tpd: Propagation Delay time tpHL: HからLに変化する場合の遅延 tpLH: 同様LからH変化

回路の動作には、時間がかかります。 図上が回路への入力信号、図下が 回路の出力信号です。立ち上がり(tr) 立ち上がり(tf)時間、遅延時間tP/tPDは 上図のように定義されています。

EX 112 21

# Exercise: EX\_112-1 p113 [STE-101-305]

- ねらい: Ring Oscillator の動作と特性を読み解く

- Example 3.1 以降 もできたら読んでおく

- ターゲット文は Regenerative Property 以降 14ライン

#### Exercise

課題文を要約してください(箇条書きでもOK、英文でも日本文でもかまいません)

- 提出はClass Web "レポート" にて木曜まで

- 毎回のレポートは、最低A41ページ以上は書いてください。余白には、 今回の授業の内容、資料についての感想や要望を記入してください。

## EX\_112-1 p113 [STE-101-305]

- Section 3.2 Definitions and Properties

- Regenerative Property

- A large noise margin is a desirable, but not sufficient requirement. Assume that a signal is disturbed by noise and differs from the nominal voltage levels. As long as the signal is within the noise margins, the following gate continues to function correctly, although its output voltage varies from the nominal one. This deviation is added to the noise injected at the output node and passed to the next gate. The effect of different noise sources may accumulate and eventually force a signal level into the undefined region. This, fortunately, does not happen if the gate possesses the regenerative property, which ensures that a disturbed signal gradually converges back to one of the nominal voltage levels after passing through a number of logical stages. This property can be understood as follows:

- An input voltage Vin (Vin ∈ "0") is applied to a chain of N inverters (Figure 3.5a). Assuming that the number of inverters in the chain is even, the output voltage Vout (N->∞) will equal VOL if and only if the inverter possesses the regenerative property. Similarly, when an input voltage Vin (Vin ∈ "1") is applied to the inverter chain, the output voltage will approach the nominal value VOH.

EX\_112\_21 EX\_112-1 p113 [STE-101-305]

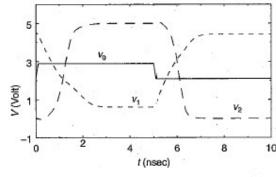

(b) Simulated response of chain of MOS inverters

#### Section 3.2 Definitions and Properties

STE-101-305

113

## Regenerative Property 再生特性 収束す

不定領域

A large noise margin is a desirable, but not sufficient requirement. Assume that a signal is disturbed by noise and differs from the nominal voltage levels. As long as the signal is within the noise margins, the following gate continues to function correctly, although its output voltage varies from the nominal one. This deviation is added to the noise injected at the output node and passed to the next gate. The effect of different noise sources may accumulate and eventually force a signal level into the undefined region. This, fortunately, does not happen if the gate possesses the regenerative property, which ensures that a disturbed signal gradually converges back to one of the nominal voltage levels after passing through a number of logical stages. This property can be understood as follows:

An input voltage  $v_{in}$  ( $v_{in} \in "0"$ ) is applied to a chain of N inverters (Figure 3.5a). Assuming that the number of inverters in the chain is even, the output voltage  $v_{out}$  ( $N \to \infty$ ) will equal  $V_{OL}$  if and only if the inverter possesses the regenerative property. Similarly, when an input voltage  $v_{in}$  ( $v_{in} \in "1"$ ) is applied to the inverter chain, the output voltage will approach the nominal value  $V_{OP}$

# EX\_112-1 p113 [STE-101-305]自動翻訳

- 再生したプロパティ

- 大きいノイズマージンは望ましい物であるけれども、not 十分な要件。シグナルがそうであると仮定するか?ノイズによって妨害されて、名目の電圧レベルと異なる。シグナルがノイズマージンにある限り、以下のゲートは、そのアウトプット電圧が名目のものと異なるけれども、正しく作動し続ける。この逸脱は、それに注入されたノイズに追加される

- アウトプットノードおよび隣のゲートに移り変わった。種々のノイズソースの効果はシグナルのレベルを蓄積し、結局、不確定な領域に押し込むことができる。もしゲートが、多くの論理的な段階を通過した後に、妨害されたシグナルが後ろに名目の電圧レベルのうちの1つに徐々に集中することを保証する再生したプロパティを所有しているならば、これは、幸運にも起こらない。このプロパティは次の通り理解できる:

- ヴィン(ヴィンe「0」)がNインバーターのチェーンに適用されるインプット電圧(数値3.5a)。もしチェーンのインバーターの数が均一ならば、もしインバーターが、再生したプロパティを所有しているならば、アウトプット電圧Vout(N->∞)はVOLと等しい。同様に、インプット電圧ヴィン(ヴィンe「1」)がインバーターチェーンに適用される時には、アウトプット電圧は額面価格VOHに近づく。

https://www.excite.co.jp/world/english/

Exercise: EX\_112-2 p116 [STE-101-308] 3.2.3から p117 [STE-101-309] (Figure 3.10)まで15line

- ・ねらい:動作の解説を読み解く(テクニカルターム、数値記号や数式が入る自動翻訳が苦手な文の例)

- Exercise

課題文を要約してください(箇条書きでもOK、英文でも日本 文でもかまいません)

- 提出はClass Web "レポート" にて木曜まで

- 毎回のレポートは、最低A41ページ以上は書いてください。 余白には、今回の授業の内容、資料についての感想や要望を記入してください。

### EX\_112-2 P116-117 [STE-101-308~9]

- 3.2.3 Performance: The Dynamic Behavior

- The propagation delay to of a gate defines how quickly it responds to a change at its input and relates directly to the speed and performance metrics. The propagation delay expresses the delay experienced by a signal when passing through a gate. It is measured between the 50% transition points of the input and output waveforms; as shown in Figure 3.10 for an inverting gate.

- Section 3.2 Definitions and Properties 117

- Because a gate displays different response times for rising or falling input waveforms, two definitions of the propagation delay are necessary. The tpLH defines the response time of the gate for a low to high (or positive) output transition, while tpHL refers to a high to low (or negative) transition. The overall propagation delay t is defined as the average of the two, (式 3.5 と図版 Figure 3.10)

- Knowledge of tp is, however, not sufficient to completely characterize circuit performance. The power consumption, noise behavior, and, indirectly, the speed of a gate are also strong functions of the signal slopes (as will become clear later in this chapter). This can be quantified with the rise and fall time measures tr and tf, which are defined between the 10% and 90% points of the waveforms (Figure 3.10).

EX\_112-2 P116-1 [STE-101-308~9]

#### 3.2,3 Performance: The Dynamic Behavior

The propagation delay  $t_p$  of a gate defines how quickly it responds to a change at its input and relates directly to the speed and performance metrics. The propagation delay expresses the delay experienced by a signal when passing through a gate. It is measured

## ction 3.2 Definitions and Properties

伝播遅延 STE-101-309 1

Figure 3.10 Definition of propagation delays and rise and fall times.

between the 50% transition points of the input and output waveforms, as shown in Figure 3.10 for an inverting gate. Because a gate displays different response times for rising or falling input waveforms, two definitions of the propagation delay are necessary. The  $t_{pLH}$  defines the response time of the gate for a low to high (or positive) output transition, while  $t_{pHL}$  refers to a high to low (or negative) transition. The overall propagation delay  $t_p$  is defined as the average of the two,  $t_p = \frac{t_{pLH} + t_{pHL}}{2}$ (3.5)

Knowledge of  $t_p$  is, however, not sufficient to completely characterize circuit performance. The power consumption, noise behavior, and, indirectly, the speed of a gate are also strong functions of the signal slopes (as will become clear later in this chapter). This can be quantified with the rise and fall time measures  $t_r$  and  $t_f$ , which are defined between the 10% and 90% points of the waveforms (Figure 3.10).

EX\_112-2 p116 [STE-101-308] 3.2.3からp117 [STE-101-309] (Figure 3.10)まで15line [自動翻訳]

#### 3.2.3 性能:動的な行動

ゲートの信号伝播時間tpは、どれほど迅速にそのインプットでそれが変化に反応し、directryをスピードと性能測定基準と関係づけるかを定義する。

#### 信号伝播時間

ゲートを通過する時にシグナルにより経験された急行遅延。それは、インプットとアウトプット波形の50%転移点の間で測定される; 裏返しgate.Iのための図3.10 ゲートが上昇のための種々の応答時間を表示するまたは

落ちてインプット波形、信号伝播時間の2つの定義がnecessary.The tpLHである

- 高い(またはポジティブ)アウトプット変遷に低さのためのゲートの応答時間を定義し、tpHLが低い(またはネガティブ)transition.The全体信号伝播時間tに高さを参照する間、2の平均として定義される、(tpLH + tpHL)tp=/2

- しかし、tpの知識は、回路performance.The電力消費量、ノイズ行動を完全に特徴付けていることについて十分ではなく、間接的に、ゲートのスピードはシグナルの斜面のまた強い機能である(として後でこの章でのクリアになる)。

- これは、波形の10%と90%ポイントの間で定義したriseと落下時間手段trとtfによって 定量化できる(図3.10)。 https://www.excite.co.jp/world/english/

## Memo

予習:次回の資料に必ず目を通しておいてください。

フォローアップURL (Revised)

http://mikami.a.la9.jp/meiji/MEIJI.htm

担当講師 三上廉司(みかみれんじ) Renji\_Mikami(at\_mark)nifty.com mikami(at\_mark)meiji.ac.jp (Alternative) http://mikami.a.la9.jp/\_edu.htm