## Science and Technology English I

Exercise 109 Meiji University 2021 (DICS Chapter-2, Transistor / MOS FET) EX 109 21.pptx 19 Slides June14<sup>th.</sup>,2022

http://mikami.a.la9.jp/mdc/mdc1.htm

#### Renji Mikami

Renji\_Mikami(at\_mark)nifty.com [mikami(at\_mark)meiji.ac.jp]

### Day 109 Exercise

- FETとトランジスタのポイント解説 この演習は最初に概容 速読をして、2回目に技術内容読込に入ります。2回目は 時間かけて読んでもいいです。

- 英文の質問を理解する

- ・学校英語力(正確に理解する必要がある)

- 技術英文から内容を読み取る

- Inbound Reading OExercise

- 英文で質問に答える

- Outbound Writing OExercise

- 長文で答えてもよい。その場合は、起承転結、序破急で書いて みよう

## 技術解説トランジスタ

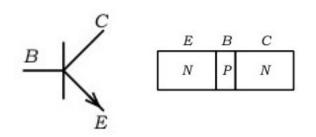

トランジスタでは、ベース電流 / B(ベース-エミッタ間電流)で / C コレクタ電流(コレクタ-エミッタ間電流)が変化する。この 比が hfe (直流電流増幅率)

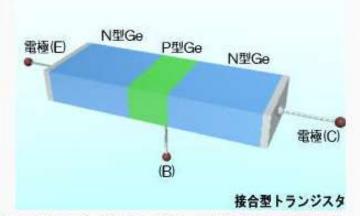

図のように、金属針(E)にプラスの電圧を、金属針(C)にマイナスの電圧をかけたとき、電極(B)の電圧次第で、E(emitter)とC(collector)の間に電流が流れたり流れなかったりすることが分かったのだ。これこそ、現在「バイボーラトランジスタ」と呼ばれているものの原型だった。今では、このトランジスタを「点接触型トランジスタ」と呼んでいる。この理論の確立にはバーディーンが大きく貢献した。

この発見を聞いたショックレーは、動作が不安定だった点接触型トランジスタを改善して、「接合型トランジスタ」を考案している。ちなみにトランジスタというのはベル研によって作られた名前だが、もともとは"transfer+resistor(電気を伝える抵抗素子)"という言葉からきている。

この三人は56年にトランジスタの発明・開発の業績を評価され、ノーベル物理学賞を受賞している。

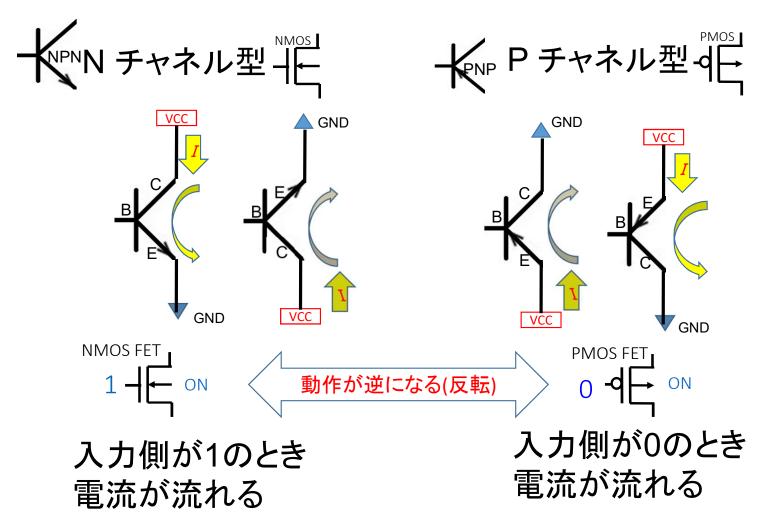

## 技術解説 MOS FET

ゲート・ソース間電圧 VGs を変化させる とドレイン電流 /D が変化する。

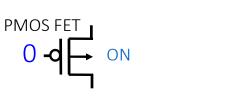

N チャンネルタイプは、Vgsが高くなると /pが増加する(エンハンスメント型)

P チャンネルタイプは、VGsが高くなるとが/D減少する(デプレッション型)

N型とP型を組み合わせた回路が CMOS(Complementary MOS)

図版引用:ウィキペディア

https://ja.wikipedia.org/wiki/MOSFET

トランジスタ 回路とFETの回路の比較トランジスタは、ベース電流でコレクタ電流がをコントロール(電流-電流制御) FETはゲート電圧でドレイン電流をコントロールする(電圧-電流制御)

# トランジスタとFETの記号

N チャネル型 P チャネル型 EとCを EとCを 逆向きに **NMOS FET PMOS FET** 入力側が0のとき 入力側が1のとき 電流が流れる 電流が流れる

## 電流の流れる方向

# Complementary回路

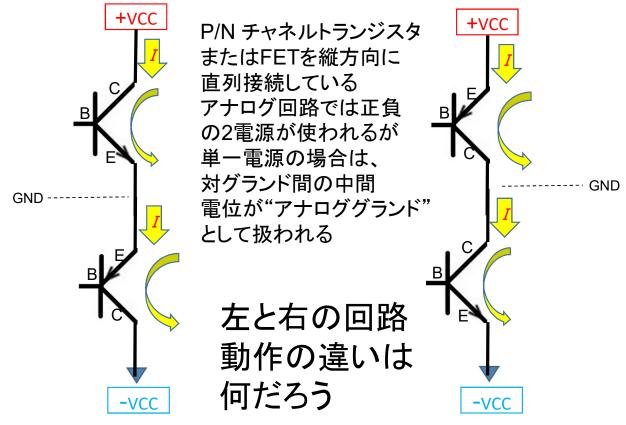

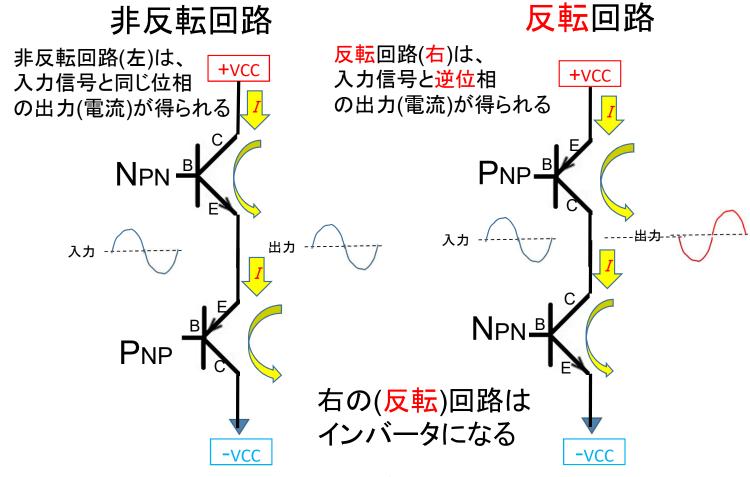

- Complementary 回路はNチャネルとPチャネル半導体を縦方向に接続して、相補的(Complementary)な回路動作をさせるもの

- まず縦方向に接続して上から下に電流を流すことを考えてみる。

- ・この方法には2通りあることが見えればよい

- ・デジタルのCMOS回路では、このうちの1つがインバー タとして使われる。

# 相補(Complementary)接続

N チャネルが+側

P チャネル型が+側

# 相補(Complementary)接続

**VDD**

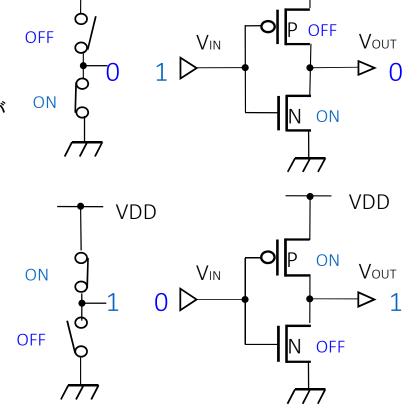

# FET(CMOS) 反転回路

Vinが1のときは、PMOSが OFF, NMOSがON. よってVOUTは0になる.

Vinが0のときは、PMOSが ON, NMOSがOFF. よってVOUTは1になる.

VDD

## Exercise: EX\_109-1 p39 [STE-101-206]

- ねらい: MOSFET の概要を読み取る

- 2.3 The MOS(FET) Transistor

- ・9ライン(2 パラグラフ)

#### Exercise

Answer following questions simply (long if you like ©).

- EX\_109-11 What is the major advantage of MOS FET?

- EX\_109-12 We focus what in this section?

- Due date : Thursday

## EX\_109-1 p39 [STE-101-206]

#### 2.3 The MOS(FET) Transistor

The metal-oxide-semiconductor field-effect transistor (MOSFET or MOS, for short) is certainly the workhorse of contemporary digital design. Its major assets are its integration density and a relatively simple manufacturing process, which make it possible to produce large and complex circuits in an economical way.

We restrict ourselves in this section to a general overview of the device and its parameters, as we did for the diode after a generic overview of the device, we present an analytical description of the transistor from a static (steady-state) and dynamic (transient) viewpoint. The discussion concludes with an enumeration of some second-order effects and the introduction of the SPICE MOS transistor models.

# 2.3 The MOS(FET) Transistor 金属-酸化物-半導体 電界効果 The metal-oxide-semiconductor field-effect transistor (MOSFET or MOS, for short) is certainly the workhorse of contemporary digital design. Its major assets are its integration density and a relatively simple manufacturing process, which make it possible to produce large and complex circuits in an economical way 事的方、定常的 We restrict ourselves in this section to a general overview of the device and its parameters, as we did for the diode—after a generic overview of the device, we present an analytical description of the transistor from a static (steady-state) and dynamic (transient) viewpoint. The discussion concludes with an enumeration of some second-order effects and the introduction of the SPICE MOS transistor models. 列挙

#### EX 109 21 Exercise: EX 109-2 p39 [STE-101-206]-p40[-207]

- ねらい: MOSFET の構造を技術的に読み取る

- 2.3.1 A First Glance at the Device

- 8ライン

#### Exercise

Answer following questions simply (long if you like ©).

- EX 109-21 Channels are separated (insulated) by what?

- EX\_109-22 What conductive material is commonly used?

- EX\_109-23 What do you think about the major difference between transistor and FET?

- Due date : Thursday

© Renji Mikami – Mikami Consulting / Meiji University 2019

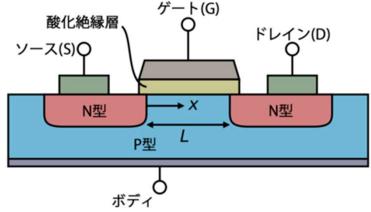

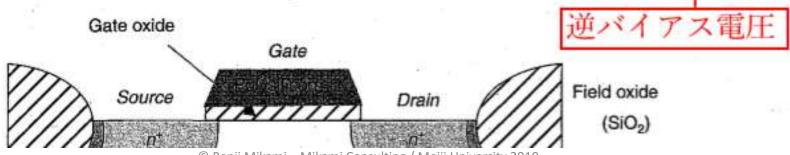

Figure 2.15

#### EX\_109-2 p39 [STE-101-206]

- 2.3.1 A First Glance at the Device

- A cross section of a typical n-channel MOS transistor (NMOS) is shown in Figure 2.15. Heavily doped *n*-type source and drain regions are implanted (or diffused) into a lightly doped *p*-type substrate (often called the *body*). A thin layer of silicon dioxide (SiO<sub>2</sub>) is grown over the region between the source and drain and is covered by a conductive material, most often polycrystalline silicon (or polysilicon, for short).

- The conductive material forms the gate of the transistor. Neighboring devices are insulated from each other with the aid of a thick layer of SiO<sub>2</sub> (called the field oxide) and a reverse-biased np-diode, formed by adding an extra p+ region, called the *channel-stop implant* (or field implant).

Figure 2.15

#### EX\_109-2 p39 [STE-101-206]

#### 2.3.1 A First Glance at the Device

THE DEVICES Chapter 2

基板

A cross section of a typical n-channel MOS transistor (NMOS) is shown in Figure 2.15. Heavily doped n-type source and drain regions are implanted (or diffused) into a lightly doped p-type substrate (often called the body). A thin layer of silicon dioxide (SiO<sub>2</sub>) is grown over the region between the source and drain and is covered by a conductive material, most often polycrystalline silicon (or polysilicon, for short). The conductive material

吉**晶** 導電性材料

40

forms the gate of the transistor. Neighboring devices are insulated from each other with the aid of a thick layer of  $SiO_2$  (called the *field oxide*) and a reverse-biased np-diode, formed by adding an extra  $p^+$  region, called the channel-stop implant (or field implant).

Figure 2.15

2022/6/14

© Renji Mikami – Mikami Consulting / Meiji University 2019

## Exercise: EX\_109-3 p40 [STE-101-207]

- At the most superficial level ~ から28行目まで

- Exercise

Answer following questions simply (long if you like ©).

- EX\_109-31 What stands for NMOS, PMOS and CMOS?

- EX\_109-32 Do you think can we make CMOS circuit by (bipolar) transistors?

- EX 109-33 Why do you think so?

提出はClass Web "レポート" にて木曜まで 毎回のレポートは、最低A4 1ページ以上は書いてください。余白には、今回の授業の 内容、資料についての感想や要望を記入してください。

## EX\_109-3 p40 [STE-101-207]

- At the most superficial level, the NMOS transistor can be considered to act as a switch. When a voltage is applied to the gate that is larger than a given value called the *threshold voltage* VT a conducting channel is formed between drain and source. In the presence of a voltage difference between drain and source, current flows between the two. The conductivity of the channel is modulated by the gate voltage—the larger the voltage difference between gate and source, the smaller the channel resistance and the larger the current. When the gate voltage is lower than the threshold, no such channel exists, and the switch is considered open.

- In an NMOS transistor, current is carried by electrons moving through an n-type channel between source and drain. This is in contrast with the *pn*-junction diode, where current is carried by both holes and electrons. MOS devices can also be made by using an *n*-type substrate and *p*+ drain and source regions. In such a transistor, current is carried by holes moving through a *p*-type channel. Such a device is called a *p*-channel MOS, or PMOS transistor. In a complementary MOS technology (CMOS), both devices are present. In a pure NMOS or PMOS technology, the substrate is common to all devices and invariably connected to dc power supply voltage. In CMOS technology, PMOS and NMOS devices are fabricated in separate isolated regions called *wells* that are connected to different power supplies. Figure 2.16 shows a cross-section of a CMOS device, where PMOS transistors are implemented in a *n*-type area embedded in a *p*-type substrate. For obvious reasons, such a fabrication approach is called an *n*-well technology.

Figure 2.15 Cross section of NMOS transistor.

断面図

変調

EX\_109-3 p40 [STE-10T-207] = 21

At the most superficial level, the NMOS transistor can be considered to act as a switch. When a voltage is applied to the gate that is larger than a given value called the threshold voltage  $V_D$  a conducting channel is formed between drain and source. In the presence of a voltage difference between drain and source, current flows between the two. The conductivity of the channel is modulated by the gate voltage—the larger the voltage difference between gate and source, the smaller the channel resistance and the larger the current. When the gate voltage is lower than the threshold, no such channel exists, and the switch is considered open.

相補的

In an NMOS transistor, current is carried by electrons moving through an n-type channel between source and drain. This is in contrast with the pn-junction diode, where current is carried by both holes and electrons. MOS devices can also be made by using an n-type substrate and  $p^+$  drain and source regions. In such a transistor, current is carried by holes moving through a p-type channel. Such a device is called a p-channel MOS, or PMOS transistor. In a complementary MOS technology (CMOS), both devices are present. In a pure NMOS or PMOS technology, the substrate is common to all devices and invariably connected to dc power supply voltage. In CMOS technology, PMOS and NMOS devices are fabricated in separate isolated regions called wells that are connected to different power supplies. Figure 2.16 shows a cross-section of a CMOS device, where PMOS transistors are implemented in a n-type area embedded in a p-type substrate. For obvious reasons, such a fabrication approach is called an n-well technology.

電源

2022/6/14

#### Memo

予習:次回の資料に必ず目を通しておいてください。

フォローアップURL (Revised)

http://mikami.a.la9.jp/meiji/MEIJI.htm

担当講師 三上廉司(みかみれんじ) Renji\_Mikami(at\_mark)nifty.com mikami(at\_mark)meiji.ac.jp (Alternative) http://mikami.a.la9.jp/\_edu.htm