# Science and Technology English I II Exercise 12 Meiji University

EX1\_Day12.pptx 10 Slides June 23rd.,2019

http://mikami.a.la9.jp/mdc/mdc1.htm

# Renji Mikami

Renji\_Mikami(at\_mark)nifty.com [mikami(at\_mark)meiji.ac.jp]

# Day 12 Exercise

- 2 グループで課題を進める(グループA/Bを明記すること)

- Aグループはなるべく英文で書く

- 3-14:

- 3-15:

- 4-14:

- 4-15:

- Bグループは日本文で書いてもよい

- 3-14:

- 3-15:

- 4-14:

- 4-15:

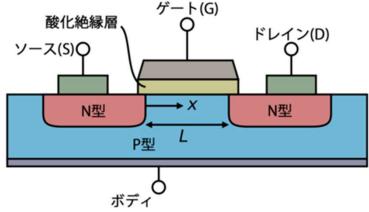

# MOS FET

ゲート・ソース間電圧 Vgs を変化させる とドレイン電流 /b が変化する。

N チャンネルタイプは、VGsが高くなると /Dが増加する(エンハンスメント型)

P チャンネルタイプは、VGsが高くなるとが/D減少する(デプレッション型)

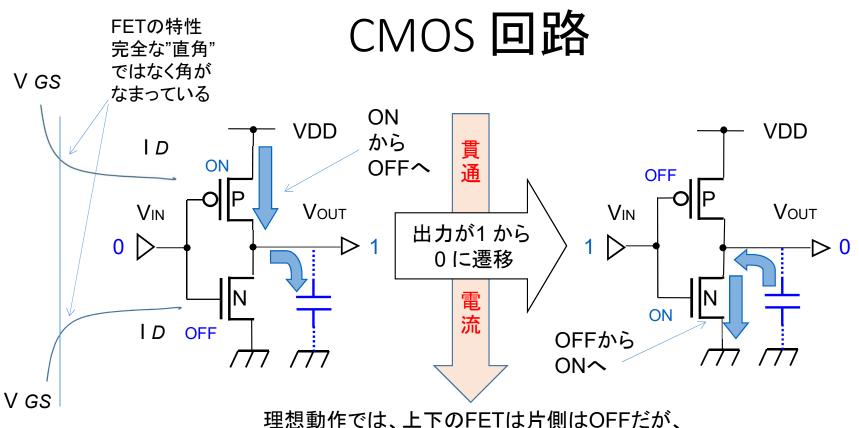

N型とP型を組み合わせた回路が CMOS(Complementary MOS)

図版引用:ウィキペディア

https://ja.wikipedia.org/wiki/MOSFET

トランジスタ 回路との比較 トランジスタでは、/ B ベース電流 (ベース・エミッタ電流)で/c コレクタ電 流(コレクタ-エミッタ)が変化する。こ の比がhfe 直流電流増幅率

理想動作では、上下のFETは片側はOFFだが、 実際は、双方がONとなり過渡的に電流が流れる

# 課題文 1-4 p116 [STE-101-308] 3.2.3から p118 [STE-101-310(Example 3.3~)の前まで]]

• ねらい:

• 1xライン(2x パラグラフ)

Execise1

Answer following questions simply (long if you like  $\odot$ ).

- 1-1 What stands for VDS and ID?

- 1-2 What is the (electric) relation between VDS and ID?

# 課題文1 p116 [STE-101-308]

### Performance: The Dynamic Behavior

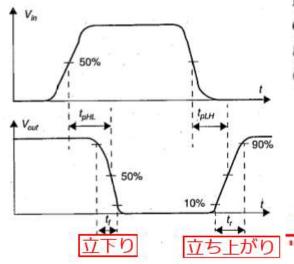

The propagation delay  $t_p$  of a gate defines how quickly it responds to a change at its input and relates directly to the speed and performance metrics. The propagation delay expresses the delay experienced by a signal when passing through a gate. It is measured

Figure 3.10 Definition of propagation delays and rise and fall times.

#### **Definitions and Properties** ction 3.2

between the 50% transition points of the input and output waveforms, as shown in Figure 3.10 for an inverting gate. Because a gate displays different response times for rising or falling input waveforms, two definitions of the propagation delay are necessary. The  $t_{pLH}$ defines the response time of the gate for a low to high (or positive) output transition, while  $t_{pHL}$  refers to a high to low (or negative) transition. The overall propagation delay  $t_p$  is defined as the average of the two.  $t_p = \frac{t_{pLH} + t_{pHL}}{2}$

Knowledge of  $t_p$  is, however, not sufficient to completely characterize circuit performance. The power consumption, noise behavior, and, indirectly, the speed of a gate are also strong functions of the signal slopes (as will become clear later in this chapter). This can be quantified with the rise and fall time measures  $t_r$  and  $t_f$ , which are defined between the 10% and 90% points of the waveforms (Figure 3.10).

(3.5)

STE-101-309

課題文 2

p117

[STE-101-309]

Knowledge of  $t_p$  is, however, not sufficient to completely characterize circuit performance. The power consumption, noise behavior, and, indirectly, the speed of a gate are also strong functions of the *signal slopes* (as will become clear later in this chapter). This

can be quantified with the rise and fall time measures t<sub>r</sub> and t<sub>f</sub>, which are defined between the 10% and 90% points of the waveforms (Figure 3.10).

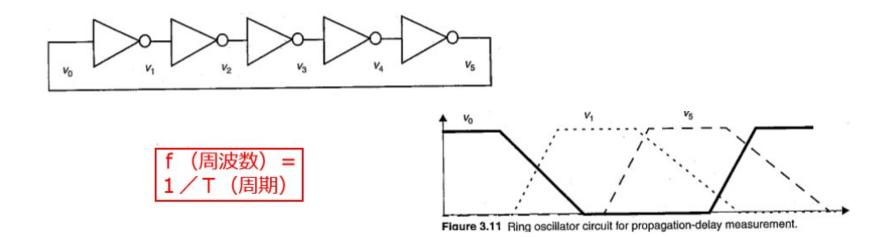

The propagation delay of a gate is a function of its fan-in and fan-out. Fan-out gates present an increased load (mostly capacitive) to the driving gate and slow its performance. The increased complexity of a gate due to a large fan-in also has a negative influence on the performance. When comparing the performance of gates in different technologies, it is important not to confuse the picture by including second-order parameters such as fan-in and fan-out. It is therefore useful to find a uniform way of measuring the  $t_p$  of a gate, so that technologies can be judged on an equal footing. The de-facto standard circuit for delay measurement is the ring oscillator, which consists of an odd number of inverters connected in a circular chain (Figure 3.11). Due to the odd number of inversions, this circuit does not have a stable operating point and oscillates. The period T of the oscillation is determined by the propagation time of a signal transition through the complete chain, or

The 50% definition is inspired the assumption that the switching threshold  $V_M$  is typically located in the middle of the logic swing.

# 課題文3

p118 [STE-101-310] STE-101-310

The period T of the oscillation is determined by the propagation time of a signal transition through the complete chain, or  $T=2\times t_p\times N$  with N the number of inverters in the chain. The factor 2 results from the observation that a full cycle requires both a low-to-high and a high-to-low transition. Note that this equation is only valid for  $2Nt_p >> t_f + t_r$  If this condition is not met, the circuit might not oscillate-one "wave" of signals propagating through the ring will overlap with a successor and eventually dampen the oscillation. Typically, a ring oscillator needs a least five stages to be operational.

## 課題文 4 p118 [STE-101-310]

無視できない

we must be extremely careful with results obtained from ring oscillator measurements. A  $t_p$  of 100 psec by no means implies that a circuit built with those gates will operate at 10 GHz. The oscillator results are primarily useful for quantifying the differences between various manufacturing technologies and gate topologies. The oscillator is an idealized circuit where each gate has a fan-in and fan-out of exactly one and parasitic loads are minimal. In more realistic digital circuits, fan-ins and fan-outs are higher, and interconnect delays are non-negligible. The gate functionality is also substantialy more complex than a simple invert operation. As a result, the achievable clock frequency on average is 50 to a 100 times slower than the frequency predicted from ring oscillator measurements. This is an average observation; carefully optimized designs might approach the ideal frequency more closely.

## Example 3.3 Propagation Delay of First-Order RC Network

Digital circuits are often modeled as first-order RC networks of the type shown in Figure 3.12. The propagation delay of such a network is thus of considerable interest.

## Memo

フォローアップURL (Revised)

http://mikami.a.la9.jp/meiji/MEIJI.htm

担当講師 三上廉司(みかみれんじ) Renji\_Mikami(at\_mark)nifty.com mikami(at\_mark)meiji.ac.jp (Alternative) http://mikami.a.la9.jp/\_edu.htm