# Science and Technology English I II Exercise 11 Meiji University

EX1\_Day11.pptx 19 Slides June 26th.,2019

http://mikami.a.la9.jp/mdc/mdc1.htm

### Renji Mikami

Renji\_Mikami(at\_mark)nifty.com [mikami(at\_mark)meiji.ac.jp]

### Day 11 Exercise

- 2 グループで課題を進める(グループA/Bを明記すること)

- Aグループはなるべく英文で書く

- 3-14:

- 3-15:

- 4-14:

- 4-15:

- Bグループは日本文で書いてもよい(英文でもよい)

- 3-14:

- 3-15:

- 4-14:

- 4-15:

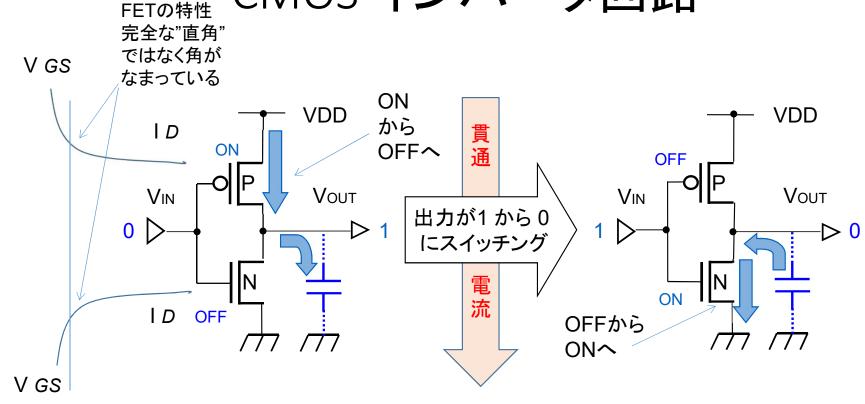

## CMOS インバータ回路

トランジスタの回路は、次の段を動作するためにB-E(ベース-エミッタ)間に電流を流し続けなければならない MOSでは次の段を駆動するために電荷をチャージすればよい。電流は、スイッチング時に流れる。

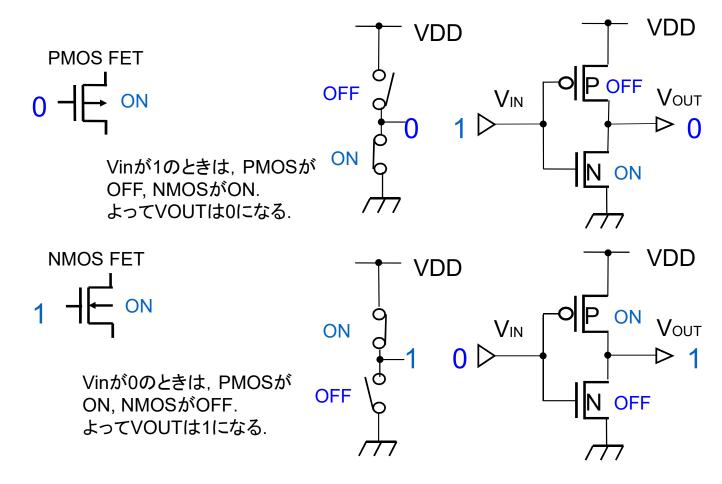

### CMOS インバータ回路

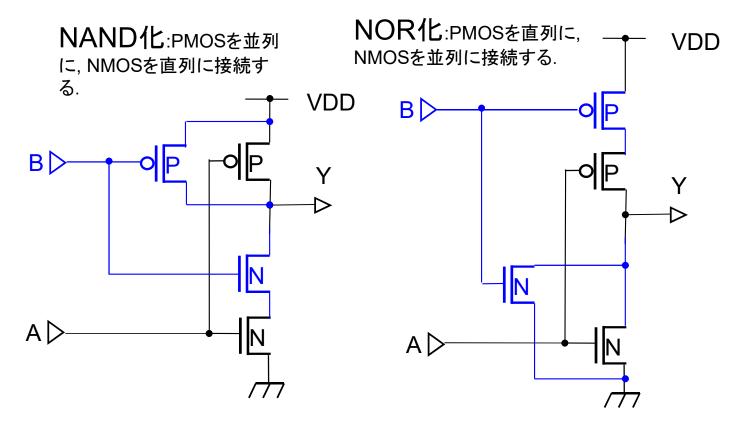

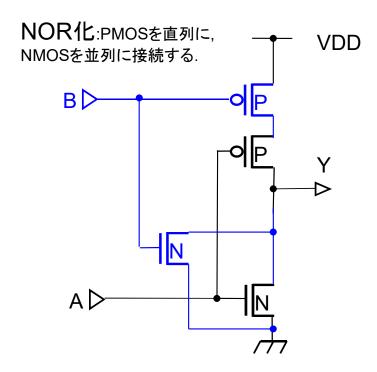

# インバータ回路のNAND/NOR化

NANDとNORでは、ドライブ段の回路が違うので特性が異なる.

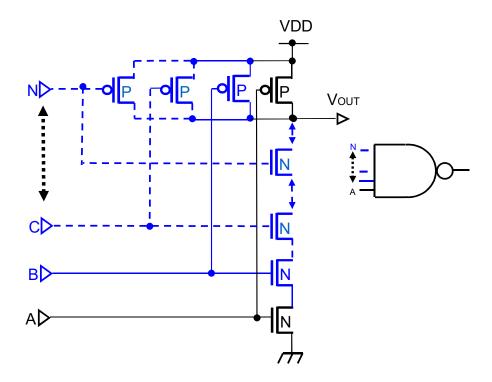

### NAND回路の多入力化

(注) FETの直並列接続によって増やせる入力数には限界がある

### NOR回路の多入力化

各自で3入力NOR回路を考えてみよう

NAND回路と同様にFETを直並列に増やすことで入力ゲート数を増やせる

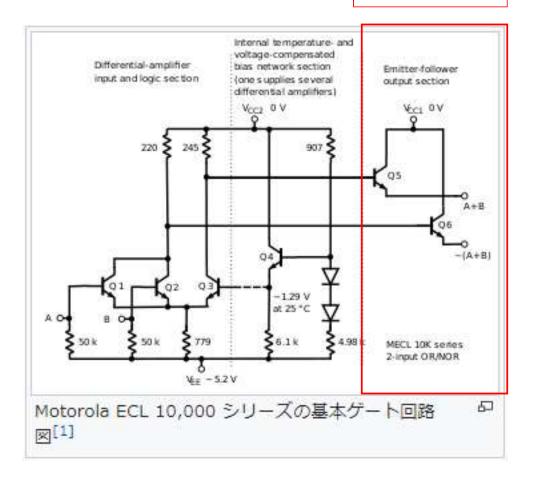

### ECL 回路

エミッタフォロア 回路

- 回路の終段(ドライバ一段)がエミッタ駆動になっている。ドライバーの役割は、次の段をドライブ(駆動)することにある。

- 通常は、増幅率を高くとれるコレクタ側で駆動するが、ドライブ・インピーダンスが高いので駆動力は小さい。

- エミッタ側でのドライブは、増幅率は1程度になるが駆動インピーダンスが低いので、負荷の大きい後段の回路を強力に駆動できる。 (TTL(Transistor Transistor Logic)型回路では、ファンアウト(駆動できる入力回路の数)を大きくとれるので有利)

CMOS Logic では、電流で駆動せず、ゲートに電荷をチャージしたり抜いたりして動作させるので大きな駆動力を必要しない。

図版引用: ウィキペディア

https://ja.wikipedia.org/wiki/エミッタ結合論理

## 課題文 1 p109 [STE-101-301]]

- ・ねらい: Inverter 回路が核になっている理由を読み取る注: CMOS インバータに着目理解、ECLは当面考えなくてもいい

- Bipolar は2極(PとNの意味) junction は接合、ECLは、 Emitter Couple Logic で高速動作だが現在特殊用途向け

- 3.1 Introduction 以下 20 (3 パラグラフ)

Execise1

Answer following questions simply (long if you like  $\odot$ ).

- <u>1-1 TBD</u>

- 1-2 TBD

#### 課題文 1 p109 [STE-101-301]

#### 3.1 Introduction

外挿する 動作と特性 109

The inverter is truly the nucleus of all digital designs. Once its operation and properties are clearly understood, designing more intricate structures such as NAND gates, adders, multipliers, and microprocessors is greatly simplified. The electrical behavior of these complex circuits can be almost completely derived by extrapolating the results obtained for inverters. The analysis of inverters can be extended to explain the behavior of more complex gates such as NAND, NOR, or XOR, which in turn form the building blocks for modules such as multipliers and processors.

The choice of a technology or a design style dramatically affects the density, performance, and the power consumption of a design. To illustrate this, we discuss in detail the behavior of static complementary CMOS and bipolar ECL inverters, which are representative gates for both MOS and bipolar technologies. Although these are not the only gate topologies in use (see Chapters 4 and 5), they are certainly the most popular at present. For each gate, we analyze the following fundamental properties:

- 頑丈

- robustness, expressed by the static (or steady-state) behavior

- 静的な(定常的)

- performance, determined by the dynamic (or transient) response

動的な(過渡的)

熱放散

heat dissipation and supply capacity requirements, set by the power consumption

The first section provides precise definitions for each of the above properties. While each of these parameters can be easily quantified for a given technology, we also discuss how they are affected by scaling of the technology. Finally, the properties of the presented gates are summarized, and some suggestions are provided on selecting a technology.

技術の微細化

定量化

### 課題文 1 p109 [STE-101-301]] 自動翻訳

- 3.1 序論

- インバーターは本当にすべてのデジタルのデザインの核である。いったんその操作とプロパティがはっきりと理解されたら、NANDゲート、加算器、係数、マイクロプロセッサーなどのより複雑な構造をデザインすることが大いに簡素化される。これらの複雑な回路の電気の行動は、インバーターのために得られた結果を補外することによってほとんど完全に引き出されうる。インバーターの分析は、係数やプロセッサなどのモジュールのための建築用ブロックを次々形成するNAND、NOR、XORなどのより複雑なゲートの行動を説明するために拡張できる。

- テクノロジーまたはデザインスタイルの選択は、デザインの密度、性能、および電力消費量にドラマチックに影響する。これを説明するために、私達は、MOSおよび双極のテクノロジーのための代表したゲートである静的な補足的なCMOSおよび双極のECLインバーターの行動を詳細に議論する。これらは、使用(4および5章を見なさい)において、唯一のゲートトポロジーではないけれども、それらは確かに、現在最もポピュラーである。個々のゲートのために、私達は以下の基本財産を分析する:

- 静的な(または定常)行動のため表現された-頑丈さ

- 動的な(または短期滞在客)反応のため決定された-性能

- 電力消費量で設定された-放熱と供給必要生産能力

- 最初のセクションは上記のプロパティのうちのそれぞれに精密な定義を提供する。与えられたテクノロジーのためにこれらのパラメータのうちのそれぞれが容易に定量化できる間、私達は、どのようにそれらがテクノロジーの縮尺によって影響されるかも議論する。最後に、提出されたゲートのプロパティが要約されて、テクノロジーを選ぶとすぐに、いくつかの提案が提供される。

https://www.excite.co.jp/world/english/

# 課題文 2 p115 [STE-101-307]

- ねらい: MOSFET のFan In Fan Out を理解する

- 2.3.3 Dynamic Behavior もできたら読んでおく

- ターゲット文は MOS Structure Capacitors 16ライン

#### Exercise

Answer following questions simply (long if you like ©).

- 2-1 TBD

- 2-2 TBD

- <u>2-3 TBD</u>

#### 課題文 2 p115 [STE-101-307]

#### Fan-In and Fan-Out

STE-101-307

劣化させる

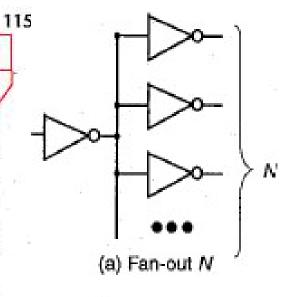

The fan-out denotes the number of load gates N that are connected to the output of the driving gate (Figure 3.7). Increasing the fan-out of a gate can affect its logic output levels. From the world of analog amplifiers, we know that this effect is minimized by making the input resistance of the load gates as large as possible (minimizing the input currents) and by keeping the output resistance of the driving gate small (reducing the effects of load currents on the output voltage). When the fan-out is large, the added load can deteriorate the dynamic performance of the driving gate. For these reasons, many generic and library components define a maximum fan-out to guarantee that the static and dynamic performance of the element meet specification.

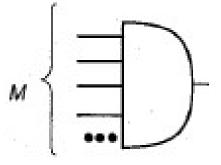

The fan-in of a gate is defined as the number of inputs to the gate (Figure 3.7b). Gates with large fan-in tend to be more complex, which often results in inferior static and dynamic properties.

Figure 3.7 Definition of fan-out and fan-in of a digital gate.

(b) Fan-in M

# 課題文 2 p115 [STE-101-307]自動翻訳

- ファンインとファンアウト

- ・ファンアウトは、ドライブゲートのアウトプットと接続されるロードゲートNの数を示す(図3.7)。ゲートのファンアウトを増大させることはそのロジックアウトプットに影響するかもしれない:レベル。アナログ増幅器の世界から、私達は、この効果が、ロードゲートのインプット抵抗を、(インプット電流を最小化する)できる限り大きくすること、およびドライブゲートのアウトプット抵抗を小さくしておくことによって最小化されると知っている(ロード電流のアウトプット電圧への効果を減らす)。ファンアウトが大きい時には、追加されたロードはドライブゲートの動的な性能を悪化できる。これらの理由のために、一般的な多くとライブラリコンポーネントは、要素の静的で、動的な性能が指定を満たしていることを保証するために、最大のファンアウトを定義する。

- ゲートのファンインはゲートへのインプットの数と定義される(数値3.7b)。大きいファンインを持つゲイツは、より複雑である傾向がある。それは、しばしば、劣っている静的な、および動的なプロパティを結果として生じる。

https://www.excite.co.jp/world/english/

# 課題文 3 p113 [STE-101-305]

- ねらい: Ring Osscilator の動作と特性を理解する

- Example 3.1 以降 もできたら読んでおく

- ターゲット文は Regenerative Property 以降 14ライン

#### Exercise

Answer following questions simply (long if you like ⊕).

- 2-1 TBD

- 2-2 TBD

- 2-3 TBD

課題文 3 p113 [STE-101-305]

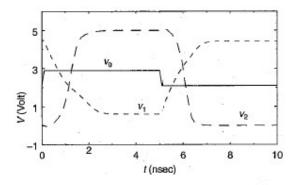

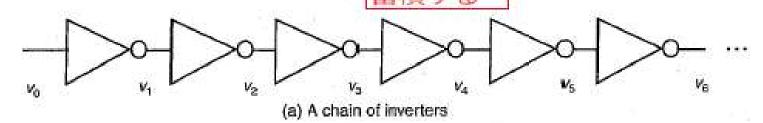

(b) Simulated response of chain of MOS inverters

#### Section 3.2 Definitions and Properties

Regenerative Property 再生特性 収束する

STE-101-305 113

不定領域

A large noise margin is a desirable, but not sufficient requirement. Assume that a signal is disturbed by noise and differs from the nominal voltage levels. As long as the signal is within the noise margins, the following gate commutes to function correctly, although its output voltage varies from the nominal one. This deviation is added to the noise injected at the output node and passed to the next gate. The effect of different noise sources may accumulate and eventually force a signal level into the undefined region. This, fortunately, does not happen if the gate possesses the regenerative property, which ensures that a disturbed signal gradually converges back to one of the nominal voltage levels after passing through a number of logical stages. This property can be understood as follows:

An input voltage  $v_{in}$  ( $v_{in} \in "0"$ ) is applied to a chain of N inverters (Figure 3.5a). Assuming that the number of inverters in the chain is even, the output voltage  $v_{out}(N \to \infty)$  will equal  $V_{OL}$  if and only if the inverter possesses the regenerative property. Similarly, when an input voltage  $v_{in}$  ( $v_{in} \in "1"$ ) is applied to the inverter chain, the output voltage will approach the nominal value  $V_{OU}$ .

# 課題文 3 p113 [STE-101-305]自動翻訳

- 再生したプロパティ

- 大きいノイズマージンは望ましい物であるけれども、not 十分な要件。シグナルがそうであると仮定するか?ノイズによって妨害されて、名目の電圧レベルと異なる。シグナルがノイズマージンにある限り、以下のゲートは、そのアウトプット電圧が名目のものと異なるけれども、正しく作動し続ける。この逸脱は、それに注入されたノイズに追加される

- アウトプットノードおよび隣のゲートに移り変わった。種々のノイズソースの効果はシグナルのレベルを蓄積し、結局、不確定な領域に押し込むことができる。もしゲートが、多くの論理的な段階を通過した後に、妨害されたシグナルが後ろに名目の電圧レベルのうちの1つに徐々に集中することを保証する再生したプロパティを所有しているならば、これは、幸運にも起こらない。このプロパティは次の通り理解できる:

- ヴィン(ヴィンe「0」)がNインバーターのチェーンに適用されるインプット電圧(数値3.5a)。もしチェーンのインバーターの数が均一ならば、もしインバーターが、再生したプロパティを所有しているならば、アウトプット電圧Vout(N->∞)はVOLと等しい。同様に、インプット電圧ヴィン(ヴィンe「1」)がインバーターチェーンに適用される時には、アウトプット電圧は額面価格VOHに近づく。

https://www.excite.co.jp/world/english/

# 課題文 3 p113 [STE-101-305]自動翻訳

- ねらい: Ring Osscilator の動作と特性を理解する

- Example 3.1 以降 もできたら読んでおく

- ターゲット文は Regenerative Property 以降 14ライン

#### Exercise

Answer following questions simply (long if you like ©).

- 2-1 TBD

- 2-2 TBD

- <u>2-3 TBD</u>

#### Memo

フォローアップURL (Revised)

http://mikami.a.la9.jp/meiji/MEIJI.htm

担当講師 三上廉司(みかみれんじ) Renji\_Mikami(at\_mark)nifty.com mikami(at\_mark)meiji.ac.jp (Alternative) http://mikami.a.la9.jp/\_edu.htm