# Computer Science Hardware Design Excise Text A DMA Feb.27th.,2017

CSHW 2017 Computer Science, Meiji University

CS\_HWA\_2017.PPT 41 Slides Renji Mikami

## ボトルネック

フォン・ノイマン・ボトルネック

プロセッサの命令セットと実行時間を比較すると、

レジスタ間のデータ転送や即値命令は、1サイクルと非常に 高速ですが、メモリの読み書き、特にメモリとメモリ間の データの転送には、非常に時間がかかります。

また周辺のハードウェアのレジスタのデータの読み書きに関しては、そのハードウェアの処理の終了を待ってから行う必要があります。

処理の終了を知る方法に、CPUが定期的にレジスタの状態を見に行くポーリングと処理が終了した時点でCPUに割り込みをかけて割り込みサービス・ルーチンに飛ばす方法があります。

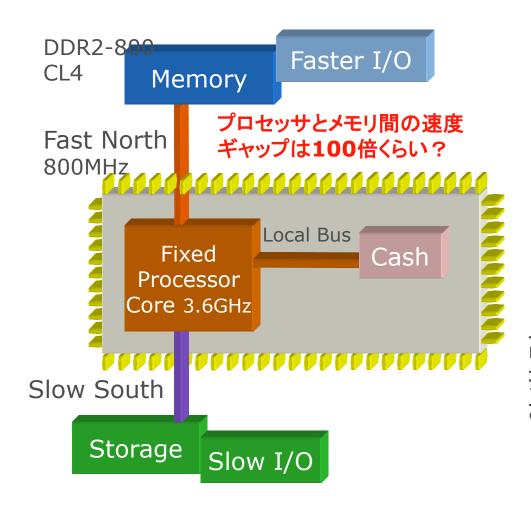

## プロセッサ・メモリ・ボトルネック

プロセッサ性能は飛躍的に高くなりましたがコンピュータシステム全体で見るとMPU性能ほどにはパフォーマンスは上がっていません

シングル・プロセッサの動作 クロックが3.6GHzあっても 外部高速インターフェース バス速度は1/5に低下します

高速インターフェースバスに 接続されたメモリ・レイテンシで さらに1/4に低下します

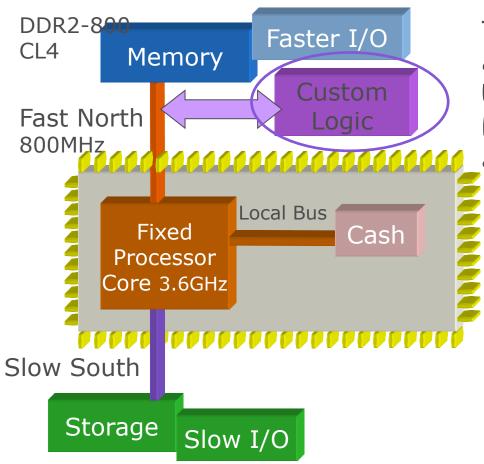

## 専用回路付加による一般的方法

プロセッサの仕様(ハードウェア と命令セット)は固定されて いますから、性能を上げるため には外部にカスタムロジックに よる専用ハードウェアを付加します。

このハードウェアが高速で動作 可能であってもメモリとの Read/WriteでMPUコアとの データのやりとりをしたのでは、 膨大なオーバーヘッドが発生 します。

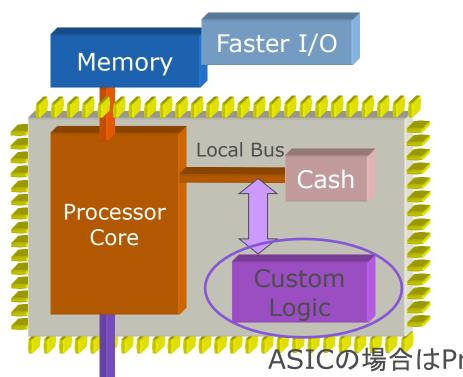

## コア内に専用回路を追加したカスタム化

さらに専用ハードウェアをIP としてダイの中に集積すれば 高集積化,高速化,ローパワー 化ができます。

このハードウェアの制御と プロセッサ間のデータの やりとりは,ダイ内部の インターフェースロジックで 決定します。

Storage Slow I/O

ASICの場合はProcessor Coreは固定機能IPの制 約がありますが性能と消費電力メリットがありま す.FPGAの場合は消費電力とダイサイズが大きくなり ますが柔軟にアーキテクチャ拡張が可能となります。

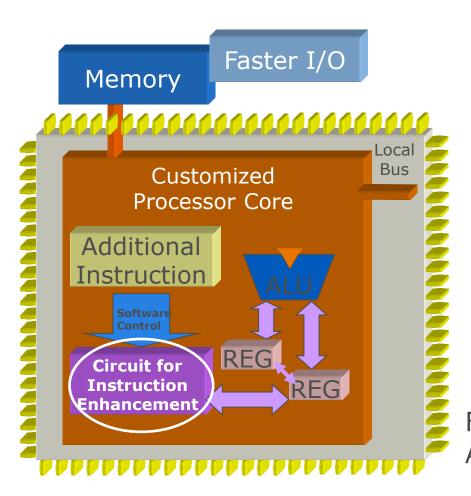

## プロセッサの命令拡張による方法

専用ハードウェア処理をプロセッサに拡張命令として実装すれば,専用回路がMPU内部アーキテクチャに実装され,ソフトウェアで制御できます。

データのやりとりは,MPUの レジスタ間となりますので オーバーヘッドがなくなり 高速,低消費電力,ダイサイズ も小型化します。

FPGAでプロトタイプ化ができ ASIC化で性能をさらに向上できます

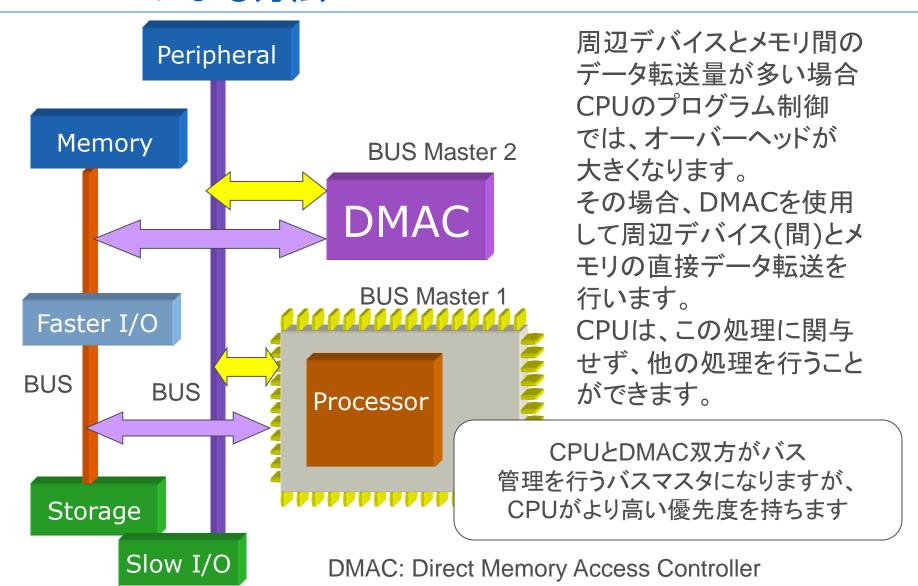

## DMAによる方法

## PSoC3/5のDMA

- PSoC3(8051-8bit)/PSoC5(ARMCortexM3-32bit)のDMAは多機能で、PSoC3ではKeil、PSoC5ではGCCコンパイラを使用しています。コンパイラによってエンディアンと上位16ビットの扱いが異なります。

- これによってDMAの使い方はやや複雑になります.

- まずは、Point to Point のデータ転送のタイプで、転送元と転送先のアドレス の設定の仕方を理解してください。

- 続いてチャネルのコンフィギュレーションの方法とTD(Transaction Descripter)のコンフィギュレーションの方法を理解するようにしてから各種のデータ転送パターンに進んでください.

- これらのソースコードは、DMAウィザードツールで自動生成できますから、 仕様から生成されたコードをもとに記述や理解を進めることができます。

- AN52705に詳しい解説があります。DMAコンポーネントデータシートを参照してください。

## PsoC3/5 のPHUB構造とDMA

周辺のH/WはPeripheral HUBを経由して相互にデータ交換 DMAはCPUを使用せずトランザクションを制御

PHUB local spoke, UDB set 0 USB. Power registers DMAのふるまいは、 CAN, (including management, Clock, Fixedconfiguration, and control function I2C, 24の各チャネル Serial wire registers). SRAM viewer (SWV). Fixed-**UDB** interface function EEPROM timers ごとに最大128 **DMAC** ステップのTD 32 bit 32 bit 16 bit 16 bit (TransactionDescripter) で記述する Spoke Peripheral HUB Arbitration HUBはBUS構造で、 Spoke1 Spoke7 16 bit 16 bit 32 bit 16 bit CPUとDMACが バスマスタになる Delta-sigma IO interface, UDB set 1 ADC Digital filter Analog registers block (DFB) Port Interrupt interface (including (優先度はCPUが高い) Control Unit (PICU). configuration, External memory and control interface (EMIF)

Figure 1. Peripheral HUB

Document No. 001-52705 Rev. \*D

# DMAデータ転送

## DMAによる(CPUを介さない)4つのデータ転送パターン

メモリー>メモリ

例: データテーブルのコピー

<mark>メモリ</mark>ー>ペリフェラル

<u>例:</u>サイン波値

テーブルを

DACに転送

ペリフェラルー><mark>メモリ</mark>

例:マスタからの

SPIデータ

ペリフェラルー>ペリフェラル

例:ADCのデータを

デジタルフィルタに転送

各ハードウェアはスポーク経由でPHUB接続

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

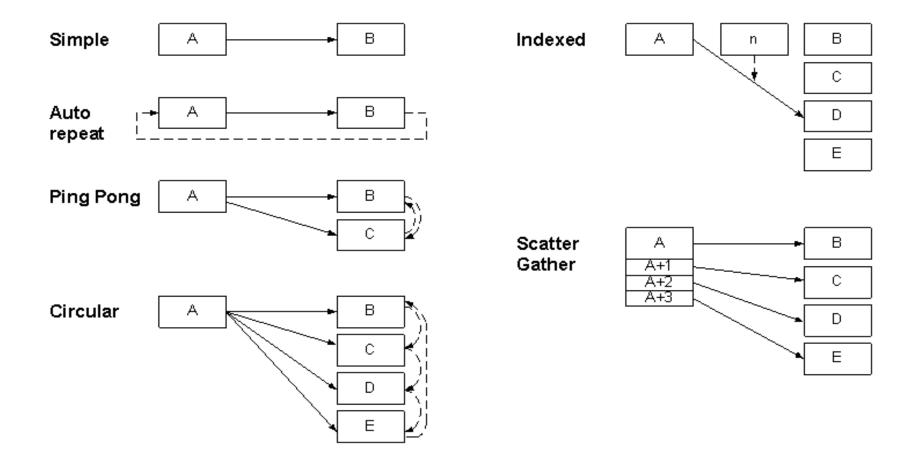

## **DMAC**

24のDMAチャネルがあり、各チャネルに8レベルのプライ オリティーを設定、プライオリティーごとに処理を割当る バンド幅が定まる

(DMAチャネルとは機能概念的なもの)

各チャネルごとにその動作をTD(Transaction Descripter, DMACの制御プログラムのようなもの)で記述する。

TDの最大は128(ステップ)

トランザクションのサイズは最大64KB

# DMAプライオリティーとバンド幅割当

各DMAチャネルにはプライオリティーを設定します。 このプライオリティーによってバスの使用率(バンド幅)が設定されます Priority 0と1は、どちらもBUSを100%占有しますが、

Priority 0が最優先 ですから、Priprity 1 のバス占有時でも Prioriyty 0が 入ってきた場合には バスのバンドはすべて Priority 0が占有します。

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

CPUとDMAは、同時に異なるスポーク経由でハードウェアにアクセスできますが、CPUのほうがDMACより高い優先度を持ちます

# Trasactionモデルの例

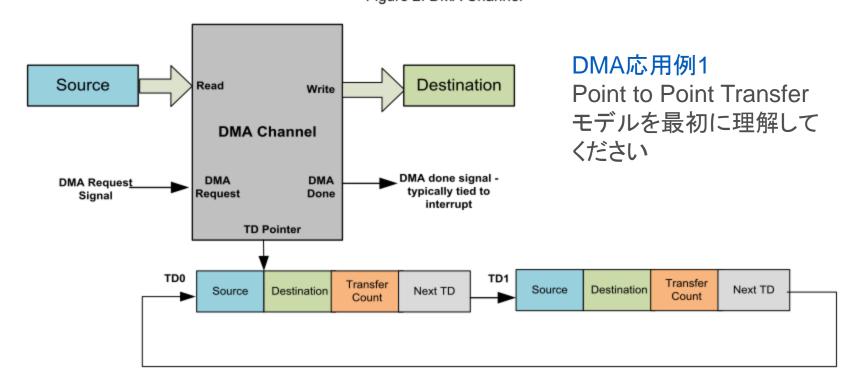

# DMAの開始と終了(DMA応用例1)

DMAチャネルは、DMA要求元のHWからの信号が DMACに入力されて開始され、DMACがDMA終了信号を出力して終了する。DMA処理は一連の処理手順で実行される Figure 2, DMA Channel

# ハードウェアのDMA開始と終了信号

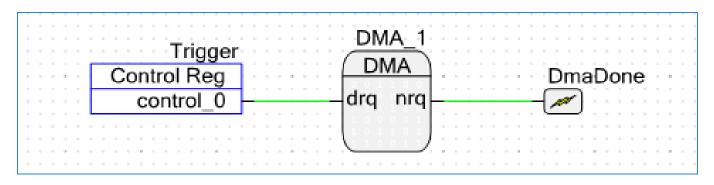

1.DMAコンポーネントを配置し,DMAスタート信号の入力結線を行う、 続いてDMA終了の出力信号を出力先のコンポーネントに接続する、続いてDMAコンポーネントのプロパティーを開いてコンフィ ギュレーションを行う

例:DMA要求元が、コントロールレジスタ0(F/Fの出力)で、この信号がDMACのdrqをアサートし、DMA転送処理が開始される。DMA転送終了時にDMACは、nrqでCPUの割り込み信号をアサートする。CPUは、現在のレジスタ状態をスタックにPUSH(書き出)し割り込み処理プログラムを実行するためにISR(Interrupt Service Routine)にジャンプする。DMA転送の間はCPUは平行して作業中の処理を継続する。

# DMA処理の手順 (Cで記述)

- 1. DMAチャネルのイニシャライズ

- 2. TDのアロケーション

- 3. TDのコンフィギュレーション TD\_Handle, 転送バイト数の設定, 記述, 次のTD, Configuration Flagの設定

- 5. イニシャルTDの選択

- 6. DMA チャネルのイネーブル

- 7. DMA転送要求のセット DMAウィザード(ツール)でコードが自動生成できる

注意: PSoC3と5では、コンパイラ(3:Keil/5:GCC)が異なるので上位 16ビットアドレスの取得方法が異なる。エンディアン Keil:B/GCC:L)も異なる。PSoC3用のコードはそのままでは、 PSoC5では動かないケースがある。(互換の記法はある)

## Channel と TDのコンフィギュレーション

Channel Configuration

Source Address(Upper 16)

転送*元*上位16ビットアドレス

Destination Address(Upper 16)

転送*先*上位16ビットアドレス

Burst Count(1 to 255)

1バーストあたり転送バイト

Request Per Burst(0 or 1)

1バースト毎に転送要求=1

First TD of channel

最初のTD

Preserve TD (0 or 1)

TD Config.REGへの状態記録=0

TDの設定-2:コンフィギュレーションフラグを参照

TD Configuration

Source Address(Lower 16)

転送*元*下位16ビットアドレス

Destination Address(Lower 16)

転送*先*下位16ビットアドレス

Transfer Count

転送バイト数(0~4095)

TD Property

アドレスのインクリメント,スワップ指定

Next TD

次のTDへのポイント

# DMA記述例: SRAM値をDACに転送

```

メモリからペリフェラルに1バイトずつ合計100バイト転送

uint8 wave[100] = {112, 百個のデータ 120};

uint8 DMA 1 Chan;

uint8 DMA_1_TD[1];

#define DMA_1_BYTES_PER_BURST 1 //1バーストあたり1バイトの転送

#define DMA 1 REQUEST PER BURST 1 //1バーストごとに転送リクエスト

#define DMA 1 SRC BASE (wave)

//転送元ソースのアドレス

#define DMA 1 DST BASE (CYDEV PERIPH BASE) //転送先ディスティネーションアドレス

/*(1) DMA Configuration for DMA 1 */

DMA 1 Chan = DMA 1 DmaInitialize(DMA_1_BYTES_PER_BURST,

DMA 1 REQUEST PER BURST,

HI16(DMA 1 SRC BASE), HI16(DMA 1 DST BASE)); //(1, 1, 0, 1)

(2)DMA_1_TD[0] = CyDmaTdAllocate();

②CyDmaTdSetConfiguration(DMA_1_TD[0], sizeof(wave), DMA_1_TD[0],

TD INC SRC AĎR):

②CyDmaTdSetAddress(DMA_1_TD[0], LO16((uint32)wave),

LO16((uint32)VDAC8_1_Data_PTR));

③CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

(3)CyDmaChEnable(DMA 1 Chan, 1);

PSoC5/GCCの場合

```

# ①DMAコンフィギュレーション

```

#define DMA 1 BYTES PER BURST 1 //1バーストあたり1バイトの転送

#define DMA 1 REQUEST PER BURST 1 //1バーストごとに転送リクエスト

#define DMA_1_SRC_BASE (wave)

//転送元ソースのアドレス

#define DMA_1_DST_BASE (CYDEV_PERIPH_BASE) //転送先ディスティネーションアドレス

/* 1DMA Configuration for DMA_1 */

DMA 1 Chan =

DMA_1_DmaInitialize(DMA_1_BYTES_PER_BURST,

DMA_1_REQUEST_PER_BURST,

HI16(DMA_1_SRC_BASE),

HI16(DMA_1_DST_BASE)); //( 1, 1, 0, 1)

バーストあたり転送バ<u>イト、1バーストごとの転送リクエ</u>ストか

どうか(YESなら1)、転送元の上位16ビットアドレス、

転送先の上位16ビットアドレスを指定(今回の値は1,1,0,1

になる

```

# ①DMAコンフィギュレーション

#define DMA 1 BYTES PER BURST 1 //1バーストあたり1バイトの転送

```

#define DMA 1 REQUEST PER BURST 1 //1バーストごとに転送リクエスト

#define DMA 1 SRC BASE (wave)

//転送元ソースのアドレス

#define DMA_1_DST_BASE (CYDEV_PERIPH_BASE) //転送先ディスティネーションアドレス

/* 1DMA Configuration for DMA_1 */

DMA 1 Chan = DMA 1 Dmalnitialize

DMA 1 BYTES PER BURST,

DMA 1 REQUEST PER BURST,

HI16(DMA_1_SRC_BASE),

HI16(DMA_1_DST_BASE)

//( 1, 1, 0, 1)

バーストあたり転送バイト、1バーストごとの転送

リクエストかどうか(YESなら1)、転送元の上位16ビットアドレ

転送先の上位16ビットアドレスを指定

(今回の値は1,1,0,1になる)

```

#### **Channel Configuration**

Source Address(Upper 16)

Destination Address(Upper 16)

転送 先上位16ビットアドレス

Burst Count(1 to 255)

1バーストあたり転送バイト

Request Per Burst(0 or 1)

1バースト毎に転送要求=1

First TD of channel

最初のTD

Preserve TD (0 or 1)

TD Config.REGへの状態記録=0

# ②TDの設定-1

```

②DMA_1_TD[0] = CyDmaTdAllocate();

//TDのアロケーション

2CyDmaTdSetConfiguration(DMA_1_TD[0],

sizeof(wave), DMA_1_TD[0], TD_INC_SRC_ADR);

//TDのコンフィギュレーション(引き数)

//CyDmaTdSetConfiguration(td,転送バイト数,次のTD,

コンフィギュレーションフラグ)

②CyDmaTdSetAddress(DMA_1_TD[0],

LO16((uint32)wave),

LO16((uint32)VDAC8_1_Data_PTR));

//CyDmaTdSetAddress(td,転送元下位16ビットアドレス.

転送先下位16ビットアドレス)

PSoC5/GCCの場合

```

# ②TDの設定-1

```

(2)DMA_1_TD[0] = CyDmaTdAllocate();

//TDのアロケーション

2CyDmaTdSetConfiguration(

DMA_1_TD[0],

sizeof(wave),

DMA 1 TD[0],

TD_INC_SRC_ADR);

//TDのコンフィギュレーション(引き数)

//CyDmaTdSetConfiguration(

td,転送バイト数,次のTD,

コンフィギュレーションフラグ)

②CyDmaTdSetAddress(

DMA_1_TD[0], LO16((uint32)wave),

LO16((uint32)VDAC8_1_Data_PTR));

//CyDmaTdSetAddress(

td,転送元下位16ビットアドレス,

転送先下位16ビットアドレス)

```

# TDの設定-2:コンフィギュレーションフラグを参照

TD Configuration Source Address(Lower 16) 転送*元*下位16ビットアドレス Destination Address(Lower 16) |転送*先*下位**16**ビットアドレス Transfer Count 転送バイト数(0~4095) TD Property アドレスのインクリメント スワップ指定 Next TD 次の**TD**へのポイント

# ②TDの設定-2:コンフィギュレーションフラグ

### .....sizeof(wave), DMA\_1\_TD[0], TD\_INC\_SRC\_ADR);

REF:DMAコンポー ネントデータシート

| TD_SWAP_EN        | エンディアン変更を実行します。                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| TD_SWAP_SIZE4     | スワップサイズ = 4 バイト                                                                                             |

| TD_AUTO_EXEC_NEXT | 現在のTDが完了すると、自動的にチェーンの次のTDが<br>トリガされます。                                                                      |

| TD_TERMIN_EN      | 「trq」入力ラインでポジティブエッジが発生すると、<br>このTDを終了します。ポジティブエッジはバースト中<br>に発生しなければなりません。その場合だけ、DMAC<br>が検知します。             |

| DMATD_TERMOUT_EN  | このTDが完了すると、TERMOUT信号がパルスを生成<br>します。注:このオプションはインスタンスに特有<br>で、インスタンス名のつぎに下線が2文字分続きます。<br>この例では、インスタンス名はDMAです。 |

| TD_INC_DST_ADR    | バーストの各データトランザクションのサイズに応じて、DST_ADRが増分します。                                                                    |

| TD_INC_SRC_ADR    | バーストの各データトランザクションのサイズに応じて、SRC_ADRが増分します。                                                                    |

# ② TDの設定-3 下位16ビットアドレス

- 2DMA\_1\_TD[0] = CyDmaTdAllocate();

- ②CyDmaTdSetConfiguration(DMA\_1\_TD[0], sizeof(wave), DMA\_1\_TD[0], TD\_INC\_SRC\_ADR);

- ②CyDmaTdSetAddress(DMA\_1\_TD[0], LO16((uint32)wave), LO16((uint32) VDAC8\_1\_Data\_PTR));

- // CyDmaTdSetAddress(td,転送元下位16ビットアドレス. 転送先下位16ビットアドレス)

VDAC8 1 Data PTR

コンポーネント・インスタンスに\_Data\_PTR をつける

# ③ チャネルのイネーブル

```

③CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

//DMAチャネルとTDのイニシャライズ

③CyDmaChEnable(DMA_1_Chan, 1);

// DMAチャネルのイネーブル化

```

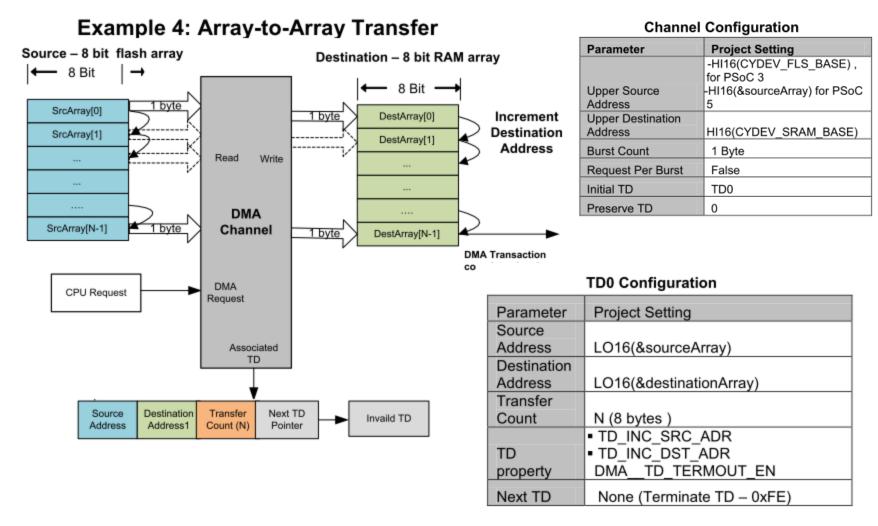

## DMAのソースとディスティネーション1-5

REF:DMAコンポーネントデータシート

#### RamからRamへ

```

uint8 DMA 1 Chan:

uint8 DMA 1 TD[1];

/* DMA Configuration for DMA_1 */

#define DMA 1 BYTES PER BURST 1

#define DMA 1 REQUEST PER BURST 1

#define DMA 1 SRC BASE (buffer1)

#define DMA_1_DST_BASE (buffer2)

DMA_1_Chan = DMA_1_DmaInitialize(DMA_1_BYTES_PER_BURST,

DMA 1 REQUEST PER BURST,

HI16(DMA_1_SRC_BASE), HI16(DMA_1_DST_BASE));

DMA 1 TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA_1_TD[0], 128, DMA_INVALID_TD, DMA_1_TD_TERMOUT_EN | TD_INC_SRC_ADR | TD_INC_DST_ADR);

CyDmaTdSetAddress(DMA 1 TD[0], LO16((uint32)buffer1),

LO16((uint32)buffer2));

CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

CyDmaChEnable(DMA_1_Chan, 1)

```

## DMAのソースとディスティネーション1-3

REF:DMAコンポーネントデータシート

#### RamからRamへ

```

uint8 DMA 1 Chan:

uint8 DMA 1 TD[1];

/* DMA Configuration for DMA_1 */

#define DMA 1 BYTES PER BURST 16

#define DMA 1 REQUEST PER BURST 1

#define DMA 1 SRC BASE (CYDEV SRAM BASE)

#define DMA_1_DST_BASE (CYDEV_SRAM_BASE)

DMA 1 Chan = DMA 1 Dmalnitialize(DMA 1 BYTES PER BURST,

DMA 1 REQUEST PER BURST,

HI16(DMA_1_SRC_BASE), HI16(DMA_1_DST_BASE));

DMA 1 TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA_1_TD[0], 128, DMA_INVALID_TD, DMA_1_TD_TERMOUT_EN | TD_INC_SRC_ADR | TD_INC_DST_ADR);

CyDmaTdSetAddress(DMA 1 TD[0], LO16((uint32)memory1),

LO16((uint32)memory2));

CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

CyDmaChEnable(DMA_1_Chan, 1);

```

PSoC3/Keilの場合

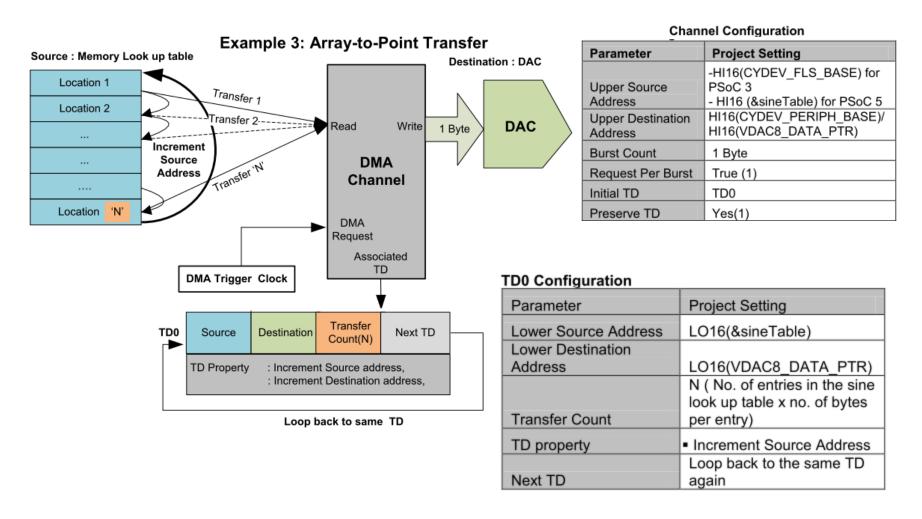

## DMAのソースとディスティネーション2-5

REF:DMAコンポーネントデータシート

```

フラッシュからDACへ:

uint8 DMA_1_Chan;

uint8 DMA_1_TD[1];

/* DMA Configuration for DMA_1 */

#define DMA_1_BYTES_PER_BURST 1

#define DMA 1 REQUEST PER BURST 1

#define DMA_1_SRC_BASE (FlashMem)

#define DMA_1_DST_BASE (CYDEV_PERIPH_BASE)

DMA_1_Chan = DMA_1_DmaInitialize(DMA_1_BYTES_PER_BURST,

DMA_1_REQUEST_PER_BURST,

HI16(DMA 1 SRC BASE), HI16(DMA 1 DST BASE));

DMA_1_TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA_1_TD[0], 64, DMA_INVALID_TD, DMA_1_TD_TERMOUT_EN | TD_INC_SRC_ADR);

CyDmaTdSetAddress(DMA_1_TD[0], LO16((uint32)FlashMem),

LO16((uint32)VDAC8_1_Data_PTR));

CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

CyDmaChEnable(DMA_1_Chan, 1);

PSoC5/GCCの場合

```

## DMAのソースとディスティネーション1-3

REF:DMAコンポーネントデータシート

```

フラッシュからDACへ

uint8 DMA_1_Chan;

uint8 DMA_1_TD[1];

/* DMA Configuration for DMA_1 */

#define DMA_1_BYTES_PER_BURST 1

#define DMA 1 REQUEST PER BURST 1

#define DMA_1_SRC_BASE (CYDEV_FLS_BASE)

#define DMA_1_DST_BASE (CYDEV_PERIPH_BASE)

DMA_1_Chan = DMA_1_DmaInitialize(DMA_1_BYTES_PER_BURST,

DMA_1_REQUEST_PER_BURST,

HI16(DMA 1 SRC BASE), HI16(DMA 1 DST BASE));

DMA_1_TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA_1_TD[0], 64, DMA_INVALID_TD,

TD INC SRC ADR);

CyDmaTdSetAddress(DMA_1_TD[0], LO16((uint32)fFashMem),

LO16((uint32)VDAC8_1_Data_PTR));

CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

CyDmaChEnable(DMA_1_Chan, 1);

PSoC3/Keilの場合

```

## DMAのソースとディスティネーション3-5

REF:DMAコンポーネントデータシート

#### 境界の条件

- 単一のDMAチャネルは64Kの境界を越えることができません。従って、DMAが64Kの境界を越えた場合、動作は警告なしに失敗します。これはPSoC 5にとってのみ重要です。その理由は、PSoC 3デバイスのメモリ空間はフラッシュの64KやRamの8Kを超えることがないからです。

- このデータ構成を使用する場合、64 Kの境界を越えないように注意してください。それには次のキーワードを利用することができます。

- \_\_attribute\_\_((section()))

- \_\_attribute\_\_((aligned()))

- これらのキーワードはいずれも、GCCの「Specifying Attributes of Variables(変数の属性指定)」セクションのヘルプで説明されています。変数を特定のセクションと位置に表示したい場合は、sectionのキーワードを使用します。コンパイラを使って変数を特定の境界に置くには、alignedのキーワードを使用します。

## DMAのソースとディスティネーション3-3

REF:DMAコンポーネントデータシート

#### フラッシュからRamへ

```

uint8 DMA 1 Chan;

uint8 DMA 1 TD[1];

/* DMA Configuration for DMA_1 */

#define DMA 1 BYTES PER BURST 1

#define DMA 1 REQUEST PER BURST 1

#define DMA 1 SRC BASE (CYDEV FLS BASE)

#define DMA_1_DST_BASE (CYDEV_SRAM_BASE)

DMA 1 Chan = DMA 1 Dmalnitialize(DMA 1 BYTES PER BURST,

DMA 1 REQUEST PER BURST,

HI16(DMA_1_SRC_BASE), HI16(DMA_1_DST_BASE));

DMA 1 TD[0] = CyDmaTdAllocate();

CyDmaTdSetConfiguration(DMA_1_TD[0], 128, DMA_INVALID_TD, DMA_1_TD_TERMOUT_EN | TD_INC_SRC_ADR | TD_INC_DST_ADR);

CyDmaTdSetAddress(DMA 1 TD[0], LO16((uint32)buf1), LO16((uint32)buf2));

CyDmaChSetInitialTd(DMA_1_Chan, DMA_1_TD[0]);

CyDmaChEnable(DMA 1 Chan, 1);

```

PSoC3/Keilの場合

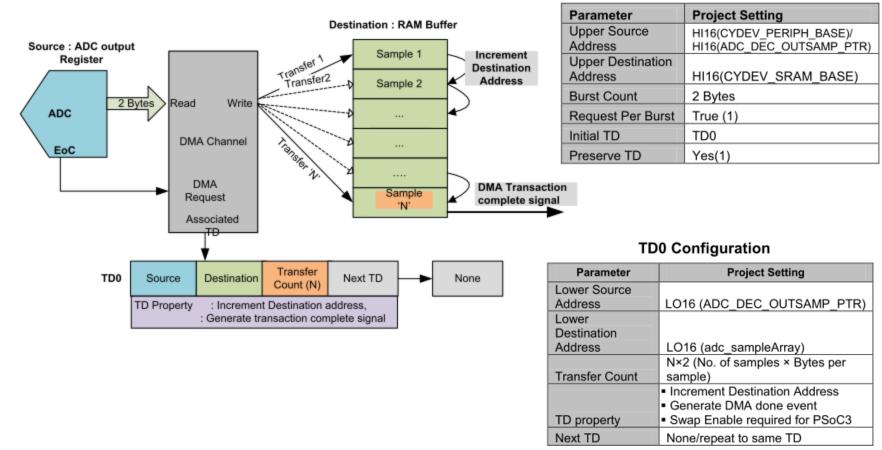

#### Example 2: Point-to-Array Transfer

This 16-bit ADC data buffering example shows how use DMA to do a point-to-array transfer.

Figure 6. Point to Array Transfer Block Diagram

#### Channel Configuration

Destination1: Example 5: Ping-Pong Buffer RAM Buffer1 Sample 1 ncrement Sample 2 Destination Address Source - ADC Output Register Figure 14. ADC-DMA Memory Sample N1 2 Byte Read Write ADC Burst N1 Burst (N1+1) ADC\_DelSig Destination2: TD1→TD2 ADC input EoC ADC DelSig RAM Buffer2 DMA to P0[2] Channel Sample 1 Increment Pin\_ADC\_In @ Sample 2 Destination DMA DMA Address ► Request DMA drq nrq eoc Associated DMA Transaction TD 8-bit complete signal Sample N2 Transfer Next TD Transfer Next TD TD0 Source Destination TD1 Source Destination Count(2×N1) Count(2×N2) Pointer Pointer

#### **Channel Configuration**

The following table shows the channel configuration, which is similar to that in Example 2.

| Parameter                 | Setting                   |

|---------------------------|---------------------------|

| Upper Source Address      | HI16(ADC_DEC_OUTSAMP_PTR) |

| Upper Destination Address | HI16(CYDEV_SRAM_BASE)     |

| Burst Count               | 2 byte                    |

| Request Per Burst         | True (1)                  |

| Initial TD                | TD0                       |

| Preserve TD               | Yes(1)                    |

Transaction 1 uses TD0, and Transaction 2 uses TD1. To attach the transactions to each other, the **Next TD** parameter of TD0 is set to TD1 and vice versa.

#### **TD0 Configuration**

| Parameter                 | Project Setting                                   |

|---------------------------|---------------------------------------------------|

| Lower Source Address      | LO16(ADC_DEC_OUTSAMP_PTR)                         |

| Lower Destination Address | LO16(adc_sampleArray1)                            |

| Transfer Count            | N1×2 ( No. of samples × Bytes per sample)         |

|                           | <ul> <li>Increment Destination Address</li> </ul> |

|                           | Generate DMA done event                           |

| TD property               | Swap Enable required for PSoC 3                   |

| Next TD                   | TD1                                               |

#### **TD1 Configuration**

| Parameter                 | Project Setting                                     |

|---------------------------|-----------------------------------------------------|

| Lower Source Address      | LO16(ADC_DEC_OUTSAMP_PTR)                           |

| Lower Destination Address | LO16(adc_sampleArray2)                              |

| Transfer Count            | N2×2 ( No. of samples × Bytes per sample)           |

|                           | <ul> <li>Increment Destination Address</li> </ul>   |

|                           | Generate DMA done event                             |

| TD property               | <ul> <li>Swap Enable required for PSoC 3</li> </ul> |

| Next TD                   | TD0                                                 |

REF:AN52705D

36

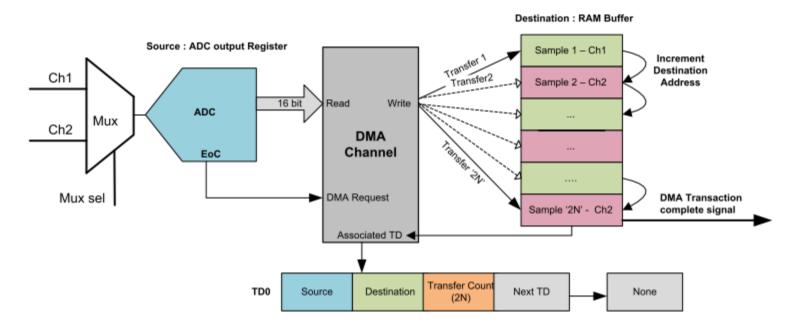

#### Example 6: Multiplexed Data Buffering

This example shows how to collect ADC data when the input to ADC is multiplexed. If a single DMA channel is used to collect multiplexed ADC data. the buffered data will be as shown in Figure 155 with channel and channel 2 data combined. But you can also keep the channel 1 and channel 2 data separate.

Figure 15. Multiplexed Data Buffering Using Single Channel

DMA channels cannot change between two transactions until the entire transfer count is finished. For this reason, multiple TDs will not work as well.. Figure 16 shows how you can use multiple DMA channels and multiplex them to move the multiplexed channel data into separate buffers.

Destination – RAM Ch1 Buffer Sample 1 Source - ADC output Register Increment Sample 2 Destination Ch1 Address 2 Byte Read ADC Mux DMA Ch2 Channel1 EoC Sample AMC DMA Transaction Request complete signal Mux sel Associated Demux Source Destination Transfer Next TD None Address Address Count (2N Destination - RAM Ch2 Buffer Sample 1 Sample 2 Destination 2 Byte Read **DMA** Channel2 Sample DMA Transaction Request complete signal Associated TD Source Destination Transfer Next TD None Count (2N) Pointer Address Address

Figure 16. Multiple DMA Channels for Buffering Multiplexed ADC Data

#### PSoC® 3: CY8C38 Family Data Sheet

#### 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TD) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line.

Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.4.4.1 Simple DMA

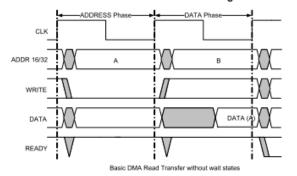

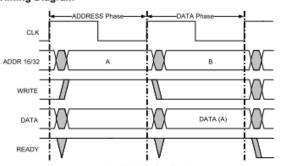

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

Figure 4-1. DMA Timing Diagram

Basic DMA Write Transfer without wait states

Document Number: 001-11729 Rev. \*T

Page 16 of 134

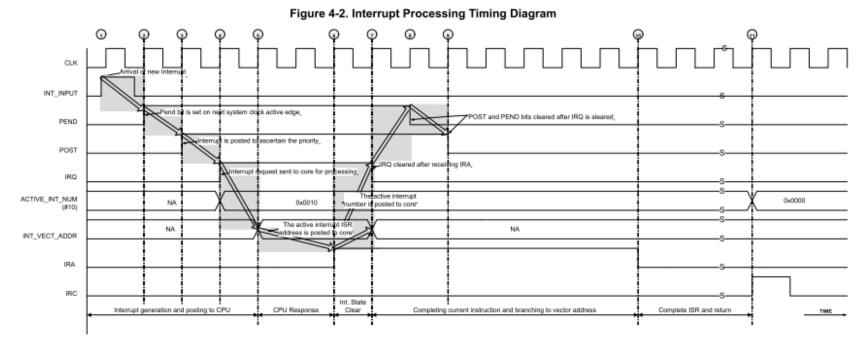

#### Notes

- 1: Interrupt triggered asynchronous to the clock

- 2: The PEND bit is set on next active clock edge to indicate the interrupt arrival

- 3: POST bit is set following the PEND bit

- 4: Interrupt request and the interrupt number sent to CPU core after evaluation priority (Takes 3 clocks)

- 5: ISR address is posted to CPU core for branching

- 6: CPU acknowledges the interrupt request

- 7: ISR address is read by CPU for branching

- 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core

- 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ISR location (Takes 7 cycles)

- 11: IRC is set to indicate the completion of ISR, Active int. status is restored with previous status

The total interrupt latency (ISR execution)

- = POST + PEND + IRQ + IRA + Completing current instruction and branching

- = 1+1+1+2+7 cycles

- = 12 cycles

Document Number: 001-11729 Rev. \*T

Page 18 of 134

## Memo

## フォローアップURL

http://mikami.a.la9.jp/meiji/meiji.htm

担当講師

ミカミ設計コンサルティング

三上廉司(みかみれんじ)

Renji Mikami(at mark)nifty.com